146255

#

An Introduction to Their Architecture, System Design, and Programming

STEPHEN P. MORSE

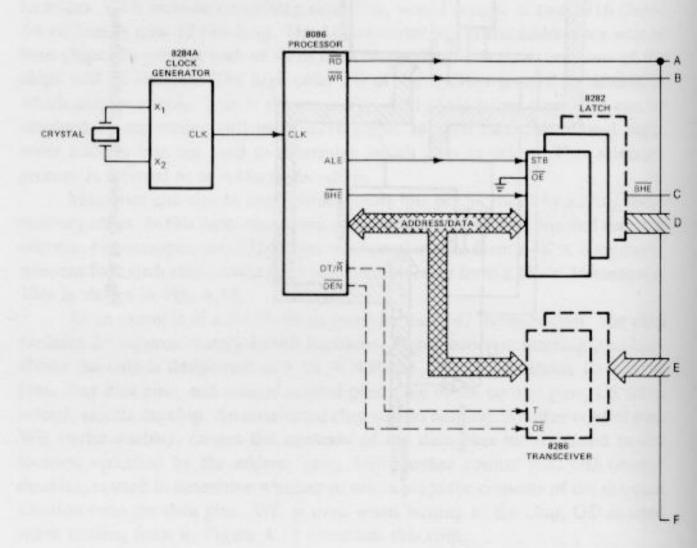

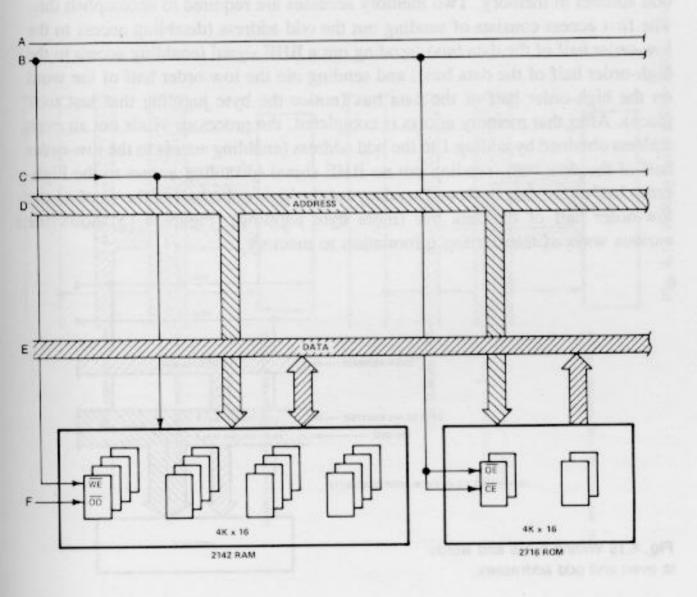

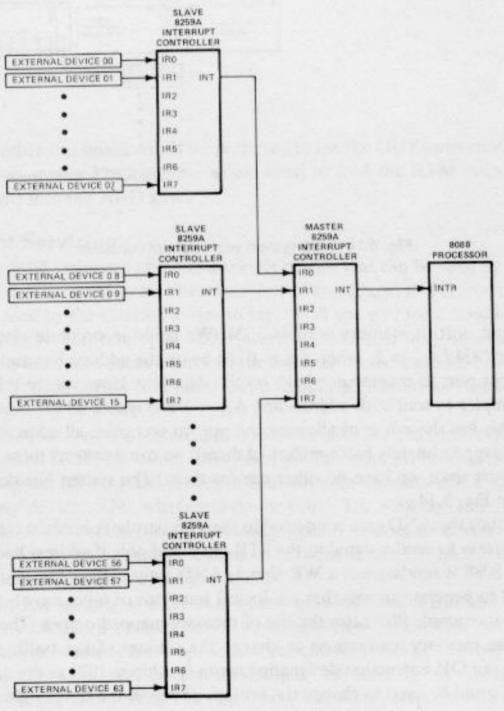

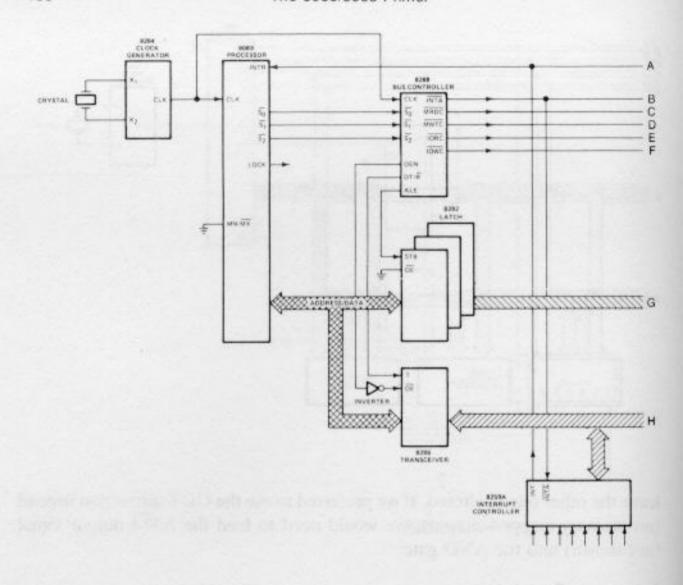

## THE 8086/8088 PRIMER An Introduction to Their Architecture, System Design, and Programming Second Edition

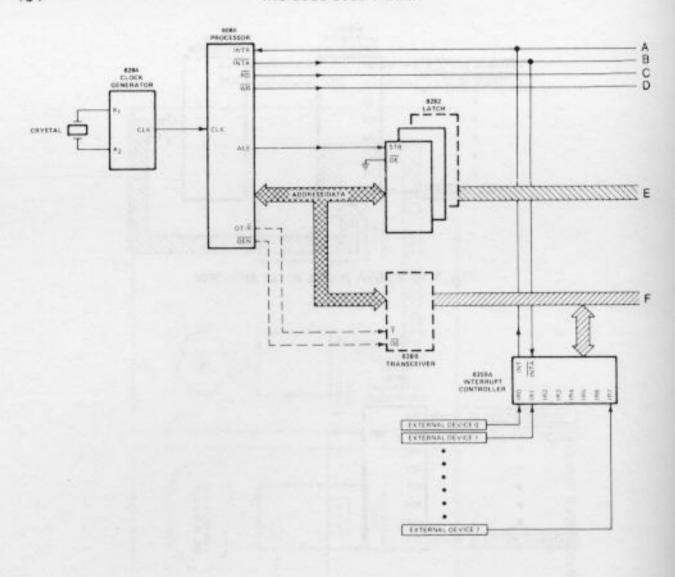

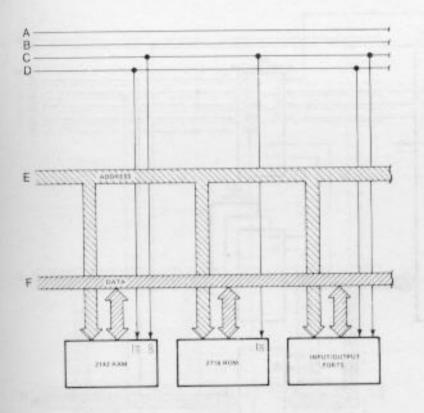

Stephen P. Morse

Written by the man responsible for the design of the 8086 microprocessor, this revised edition has been updated to provide novices and professionals alike with a thorough introduction to Intel's 8086 and 8088 microprocessors.

After a general introduction to computers and microprocessors, with emphasis on the 8086, the book discusses architecture: the machine organization of the 8086/8088, covering register and memory structure, addressing modes, and the 8086/8088 instruction set.

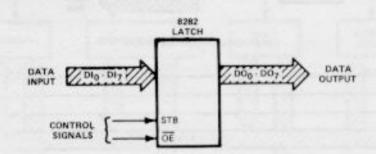

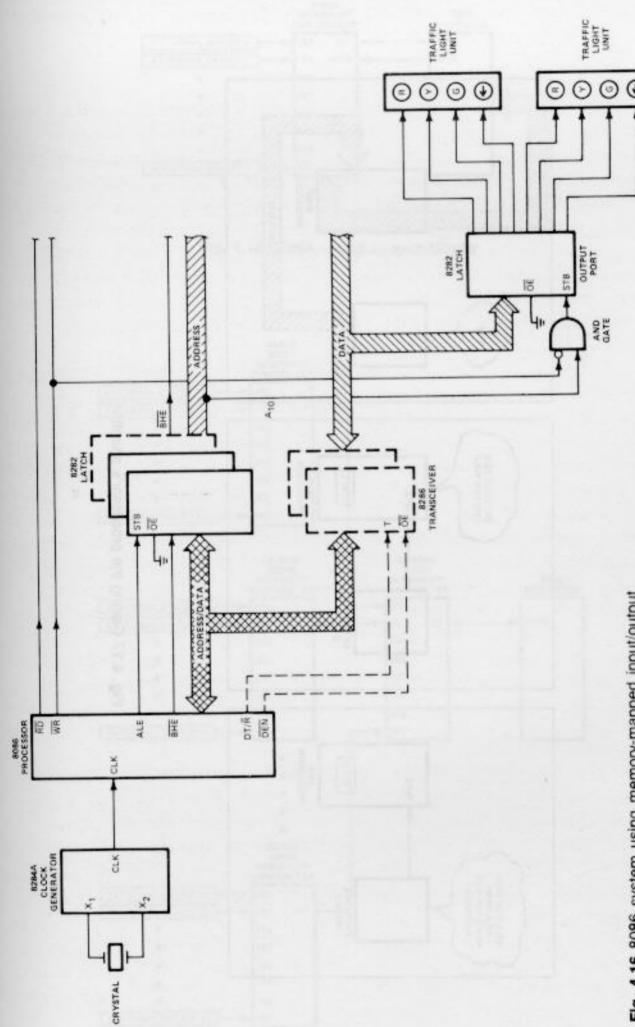

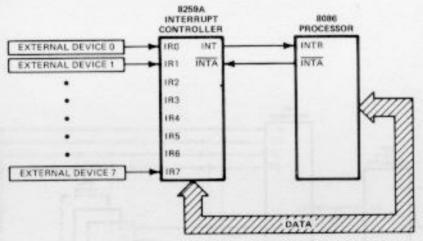

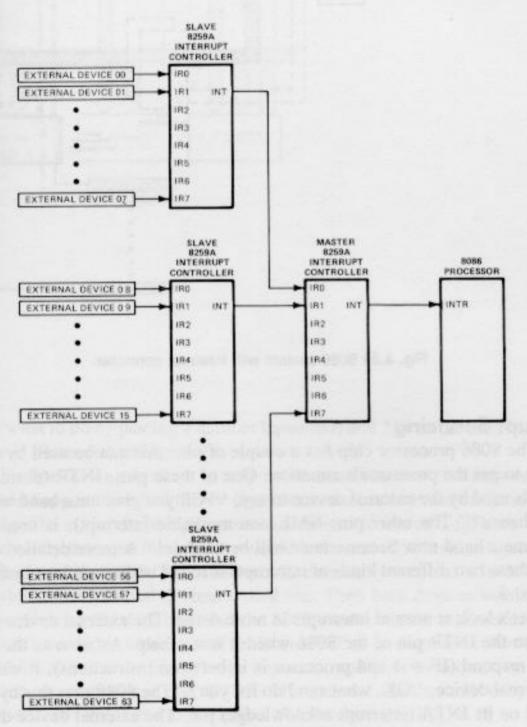

The section on system design features a new chapter highlighting the 8088—how to combine the chip with other components to form a complete system—and includes bus structure, address latching, data amplifying, measuring time, memory units, input/output ports, interrupt servicing, and bigger systems. The 8086 and 8088 are also considered as circuit components, and the design fundamentals of an 8086- or 8088-based system are discussed.

The book concludes with a discussion of programming. In addition to chapters on a low-level programming language, ASM-86, and a high-level language, PL/M-86, a new chapter examines the Pascal language.

A Division of Howard W, Sams & Company 4300 West 62nd Street Indianapolis, Indiana 46268 USA

\$19.95/046255 ISBN: 0-8104-6255-9

## The 8086/8088 Primer

An Introduction to Their Architecture, System Design, and Programming

SECOND EDITION

STEPHEN P. MORSE

#### HAYDEN BOOKS

A Division of Howard W. Sams & Company 4300 West 62nd Street Indianapolis, Indiana 46268 USA

#### To Megan

© 1980 and 1982 by Hayden Books A Division of Howard W. Sams & Co.

SECOND EDITION NINTH PRINTING—1987

Instruction Mnemonics copyright by Intel Corp., 1978

All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 0-8104-6255-9

Printed in the United States of America

#### Preface

This book is an introduction to the 8086 microprocessor. It describes the 8086 architecture, shows how to design a system incorporating an 8086, and discusses how to write programs that run on the 8086. Since the treatment is detailed and relies heavily on examples and illustrations, it can be useful to both the computer novice and the computer professional.

The book is composed of three main topics—8086 architecture, 8086 system design, and 8086 programming. The architecture is broken down into 8086 machine organization (register and memory structure, addressing modes), covered in Chap. 2, and 8086 instruction set, covered in Chap. 3. The 8086 and 8088 system designs in Chaps. 4 and 5 show how to put these microprocessors together with other components to form a complete microcomputer system. Programming is divided into 8086 assembly-language programming (Chap. 6) and 8086 high-level-language programming (Chaps. 7 and 8).

The first chapter is intended to bring a heterogeneous group of readers up to a common level of knowledge about computers and microcomputers. If you already have that knowledge and you're anxious to learn about the

8086, skip ahead to Chap. 2.

The first edition of this primer did not discuss the language Pascal because no 8086 Pascal compilers were available at the time of that writing. The only 8086 high-level language then in existence was PL/M. Today several 8086 Pascal compilers exist, and each language is now covered in

its own chapter (Chap. 7 for PL/M and Chap. 8 for Pascal).

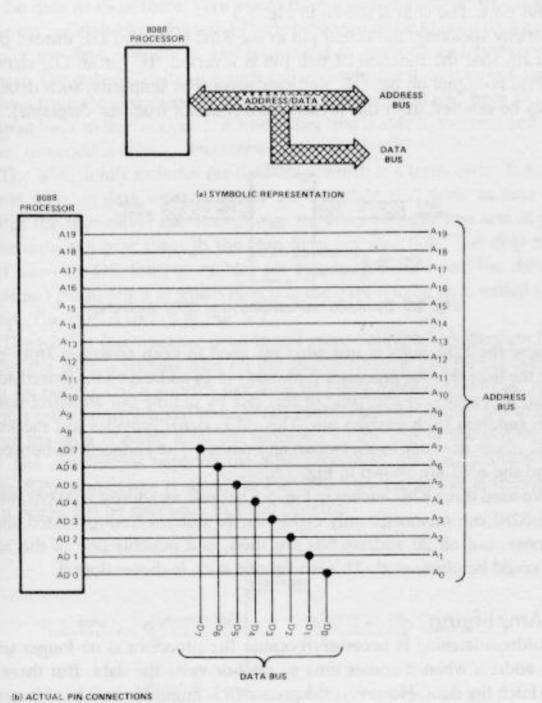

Another topic not in the original edition is the 8088. The primary difference between the 8086 and 8088 processors is the amount of data that each can transfer to and from the outside world at one time—the 8086 can transfer 16 bits, whereas the 8088 can transfer only 8 (both processors can manipulate 16 bits of data internally). This difference has its greatest impact on system design, and hence each processor has its own system design chapter (Chap. 4 for the 8086 and Chap. 5 for the 8088). All other chapters are applicable to both processors, although, for convenience, only the 8086 is mentioned (constantly writing 8086/8088 is awkward).

I would like to thank those same people whom I thanked in the original edition (plus a few new ones) who contributed many hours of their own time to reading the drafts and finding my numerous errors. They are Richard Altmaier, John Crawford, Rodney Farrow, Joseph Friedrich, Stephen Hanna, Marek Jeziorek, Jeffrey Katz, Phillip Kaufman, John Palmer,

Samuel Quiring, Andrew Rabinowitz, Joseph Sharp, and Thomas Wilcox. A special thanks goes to Alice Morse, my mother and lifelong proofreader.

Finally, let me thank my wife Anita for graciously relinquishing her place on the dedication page to our daughter, Megan, who should be born at about the same time as this book is published.

STEPHEN P. MORSE

San Francisco, California

#### **Foreword**

In 1972, Intel announced the 8008, the first commercially available 8-bit microprocessor, which ultimately led to the 8080, the industry standard microprocessor. When they were introduced, some observers wondered what these new gadgets could be used for. To date, over three million have been used, not counting support and peripheral circuits, for thousands of different uses from telephone switching systems to TV games.

Since 1972, the microprocessor revolution has opened a multitude of component and system applications, from one-device engine control to single-board computers for complex industrial control tasks. In 1978, Intel introduced the first high-performance 16-bit microprocessor, the 8086.

The thrust of the 8086 has always been to help users get their products to market faster using compatible software, peripheral components, and system support. In this "family" concept, the CPU is the heart of a system, extending to interfaces, memories, peripherals, communications, computer systems, and software. This 8086 family consists of several CPUs as well as complete support for bus control. For example, Intel provides the 8088 CPU, which utilizes the same 16-bit internal architecture as the 8086 but has an external 8-bit bus, thus bridging the gap between 8-bit and 16-bit processors. The 8089 is designed as a special high-performance I/O processor for offloading and processing in parallel the host CPU (also available is the 8086-2, an 8-MHz version of the standard 5-MHz 8086). The 8086 family was designed as a multiprocessing family such that a system consisting of multiple processors is easily implemented, supported not only by the 8086 family of CPUs but also by "family" bus support circuitry. The 8289 Bus Arbiter, in conjunction with the 8288 Bus Controller, provides a powerful and efficient means of arbitrating multiple CPUs residing on a shared system bus. Whether designing a single CPU system or a high-performance multiple processor system, the 8086 family supports the "total system" solution.

At first glance, the complexity of 16-bit microprocessor system design seems to govern the choice between diverse component products. The key issue is actually synergism. The ease of use among Intel products offers building-block solutions to entire system design problems. One can use the same components for designing a single microprocessor-based system with

one common bus or a very powerful multiple processor system with a host of shared resources.

With the common thread of compatible architecture, user language (like PLM or PASCAL), and a series of development systems that support each and every programmable device, Intel has endeavored to ease the design task for engineers working on microprocessor-based systems, both large and small.

We recommend Stephen Morse's book to those interested in using the 16-bit universe as the solution to their design problems.

read of campions the regimes about review I south all anomal at come

DAVE GELLATLY

Microprocessor Marketing Manager

Intel Corporation

### Contents

| 1. | Introduction                                                                                                                                                                                                  | 1  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | Computer Overview, 1<br>Data Formats, 3<br>Stacks, 7                                                                                                                                                          |    |

|    | 8086 Memory Utilization (A Sneak Preview), 8<br>The Microcomputer Story, 8                                                                                                                                    |    |

| 2. | 8086 Machine Organization                                                                                                                                                                                     | 12 |

|    | Overview, 12 Memory Structure, 13 Memory Segmentation, 14 Input/Output Structure, 18 Register Structure, 18 Instruction Operands and Operand-Addressing Modes, 23 Comments about Operand-Addressing Modes, 30 |    |

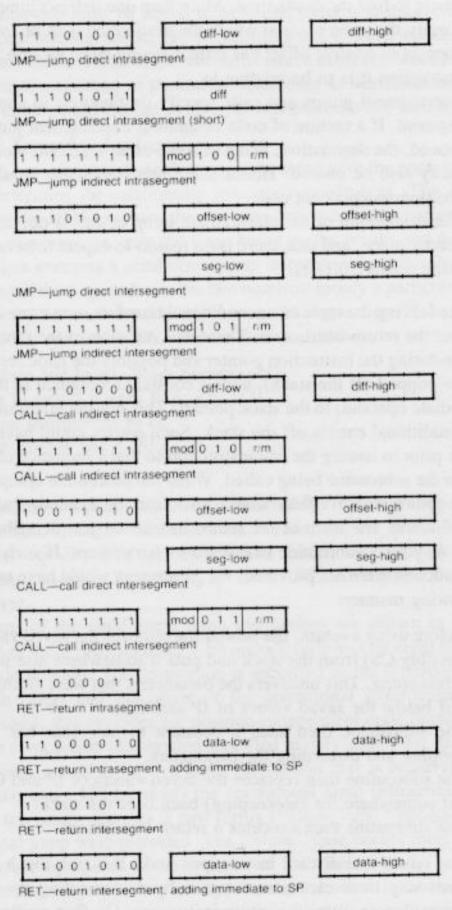

| 3. | 8086 Instruction Set                                                                                                                                                                                          | 34 |

|    | Data Transfer Instructions, 34 Arithmetic Instructions, 45 Logical Instructions, 62                                                                                                                           |    |

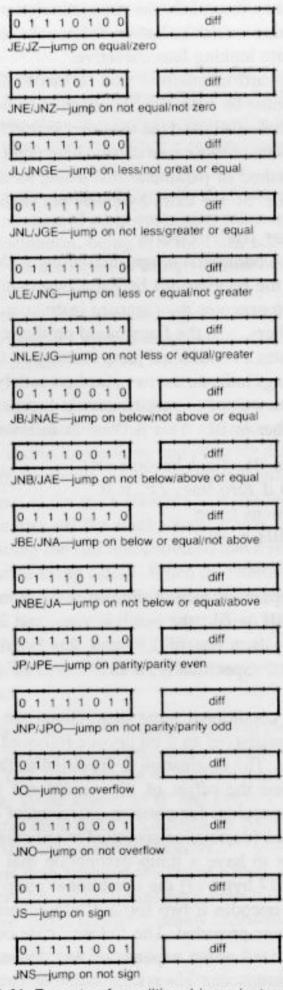

|    | String Instructions, 66 Unconditional Transfer Instructions, 74 Conditional Transfer Instructions, 79                                                                                                         |    |

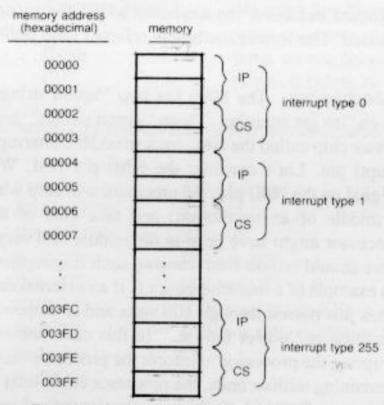

|    | Interrupts, 82 Flag Instructions, 90 Synchronization Instructions, 91                                                                                                                                         |    |

|    | A Postscript on Prefixes, 94<br>Flag Settings, 95                                                                                                                                                             |    |

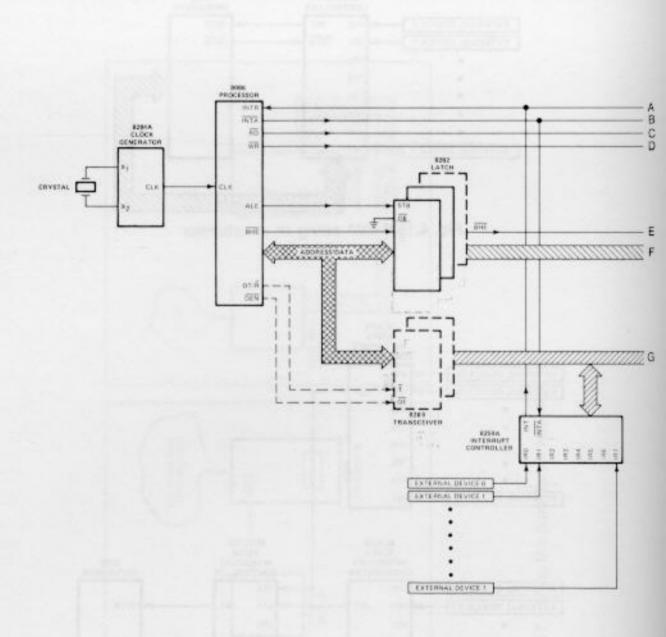

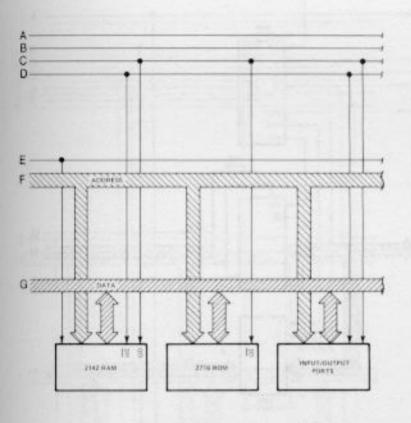

| 4. | 8086 System Design                                                                                                                                                                                            | 99 |

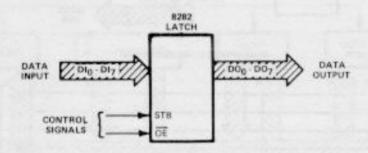

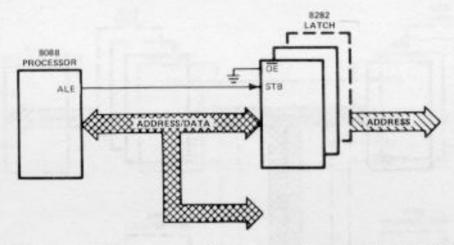

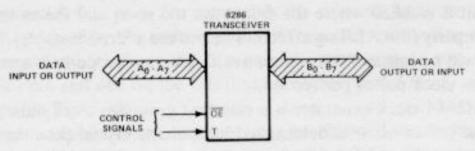

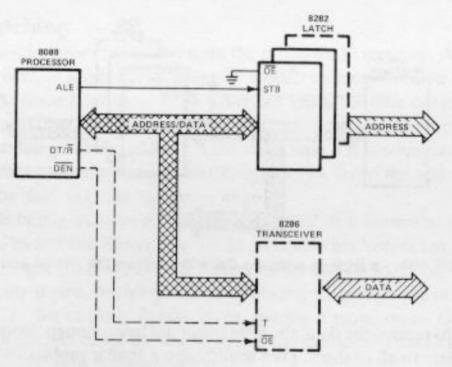

|    | Bus Structure, 99 Address Latching, 102 Data Amplifying, 102 Measuring Time, 104 Memory Units, 105                                                                                                            |    |

|    | Input/Output Ports, 112 Interrupt Servicing, 116 Bigger Systems, 119 Summary, 120                                                                                                                             |    |

207

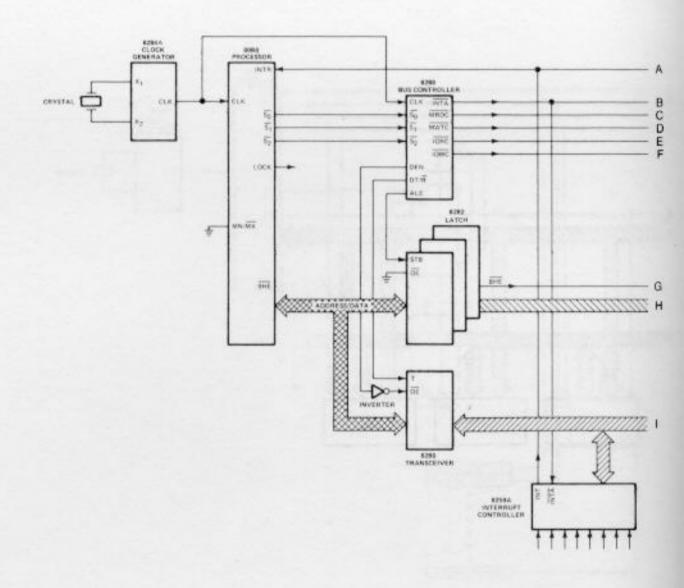

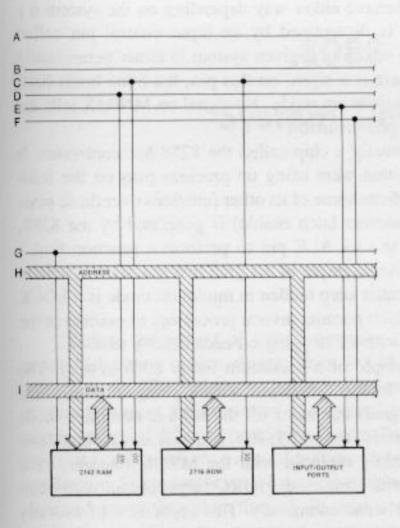

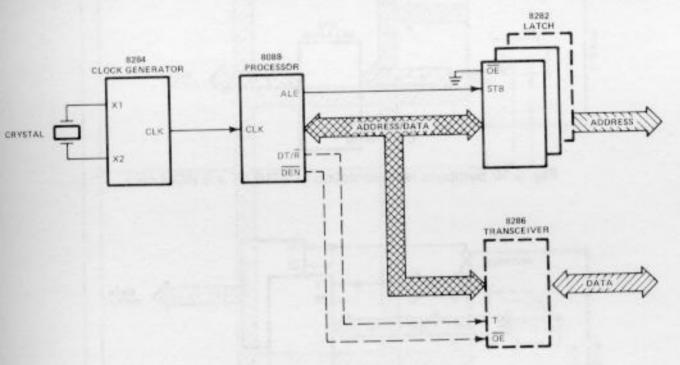

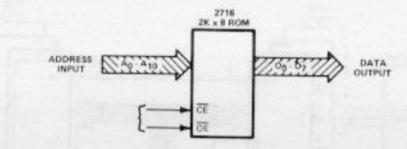

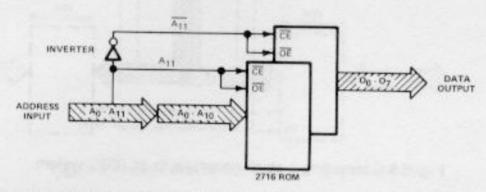

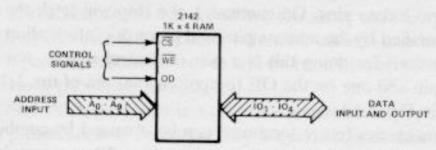

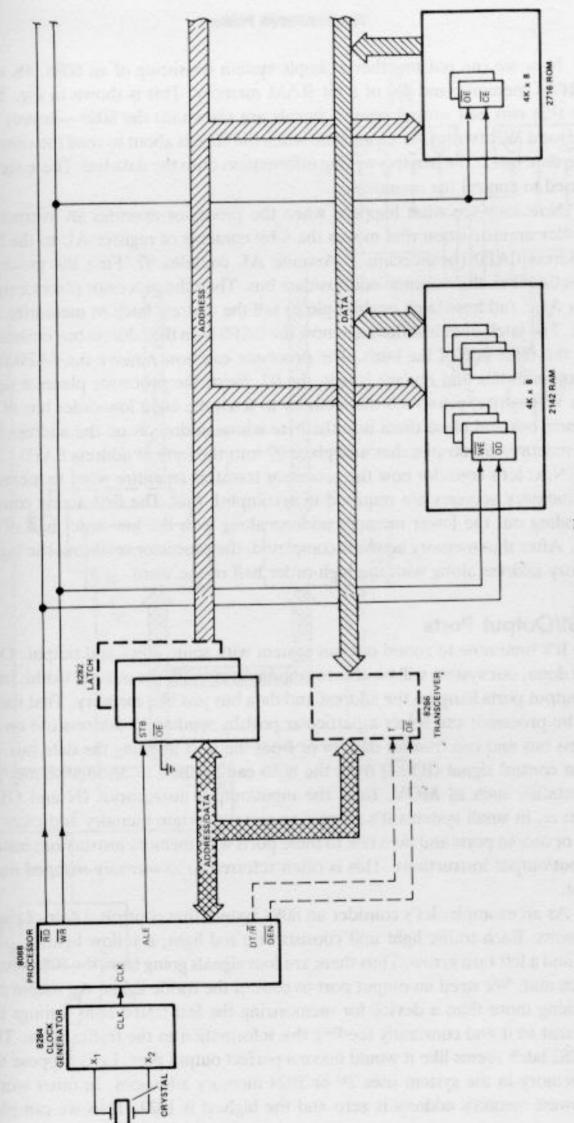

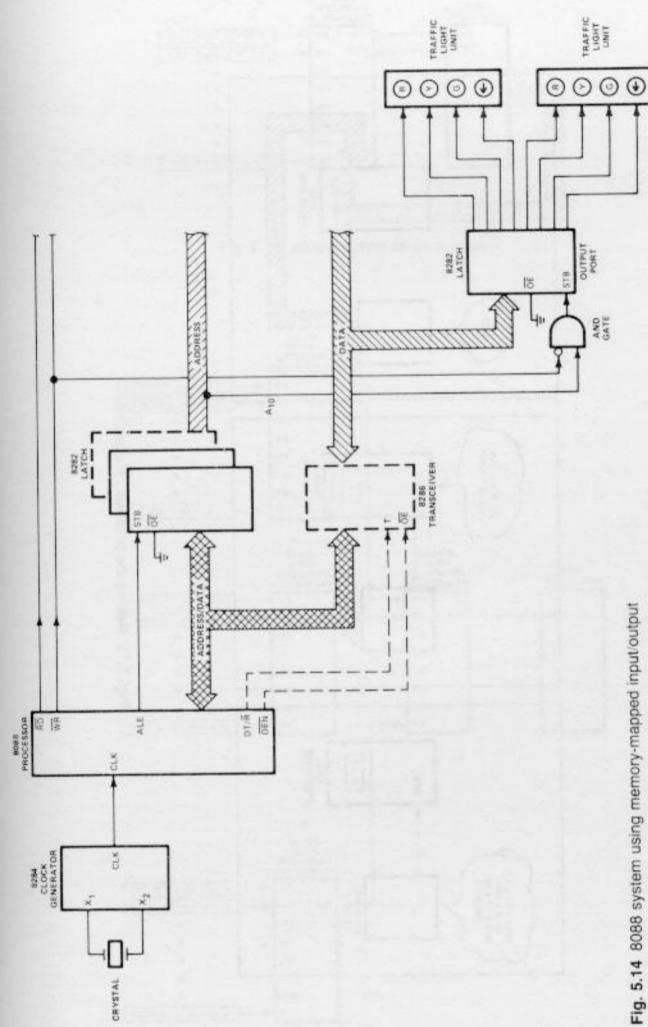

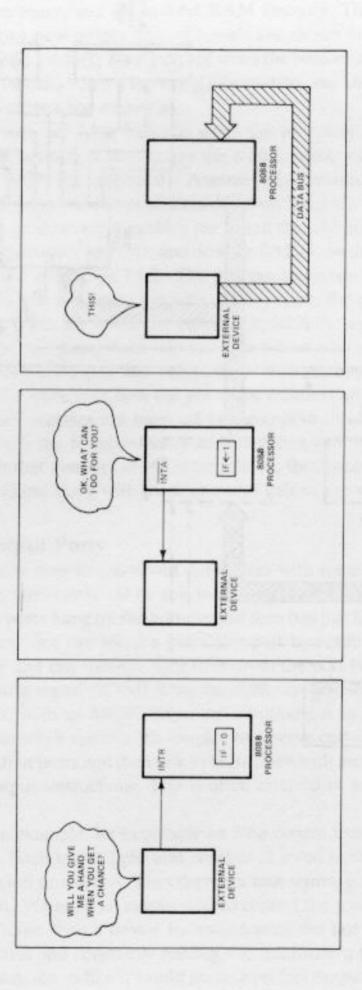

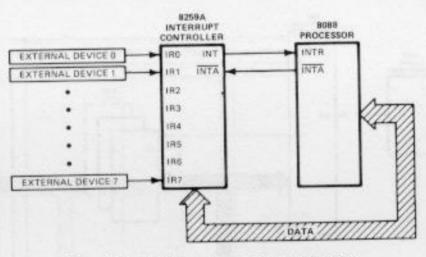

#### 5. 8088 System Design

Bus Structure, 121 Address Latching, 124 Data Amplifying, 124 Measuring Time, 126 Memory Units, 127 Input/Output Ports, 130 Interrupt Servicing, 135 Bigger Systems, 137 Summary, 138

#### 6. 8086 Assembly-Language Programming

Object Code and Source Code, 139

Symbolic Names, 141

A Complete Program, 142

Structure of ASM-86 Programs, 143

Tokens, 145

Expressions, 148

Statements, 151

Directive Statements, 152

Instruction Statements, 164

Examples, 168

In Conclusion, 170

#### 7. 8086 High-Level-Language Programming (PL/M)

Who Needs High-Level Languages?, 171

Structure of PL/M-86 Programs, 173

Tokens, 175

Expressions, 177

Statements, 179

Executable Statements, 180

Declarative Statements, 185

Procedures, 192

Block Structure and Scope, 198

Input and Output, 200

Modular Programming, 201

Tying It All Together, 203

In Conclusion, 205

#### 8. 8086 High-Level-Language Programming (Pascal)

Who Needs High-Level Languages?, 207 Structure of Pascal Programs, 208

Tokens, 210 Expressions, 213 Definitions, Declarations, and Statements, 216 Statements, 217 Definitions and Declarations, 224 Types, 227 Simple Types, 227 Structured Types, 230 Pointer Types, 239 Procedures and Functions, 241 Block Structure and Scope, 246 Input and Output, 249 Aside about Standard Pascal, 251 Separate Compilations, 251 Tying It All Together, 255 Summary, 257

| 9. References                       | 258 |

|-------------------------------------|-----|

| Appendix A: Instruction Set Summary | 260 |

| Appendix B: Opcode Space            | 265 |

| Appendix C: ASCII Codes             | 268 |

| Index                               | 269 |

1

#### Introduction

The aim of this first chapter is to gain a technical and historical perspective on microcomputers in general and the 8086 in particular. Microcomputers are not unlike any other computer except in size. So we'll start by summarizing the fundamentals of computers and then describe the evolutionary process that led to the microcomputer. Finally, we'll show where the 8086 fits into the picture.

Computer Overview

Before we talk about a microcomputer, let's briefly summarize the notion of a computer. Besides serving as a review, this section will introduce some of the terms and concepts used throughout the book.

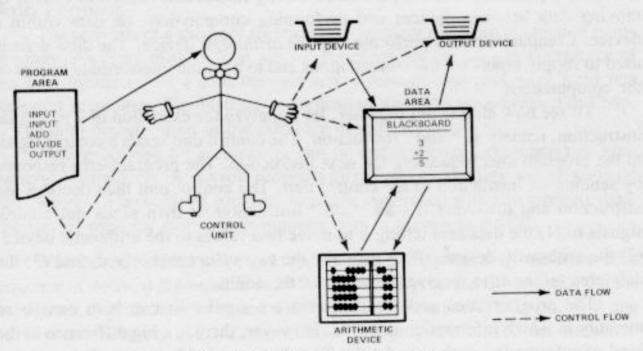

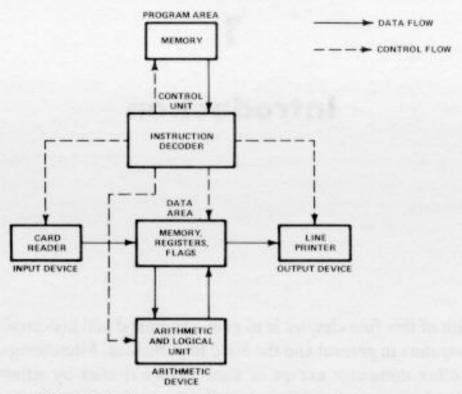

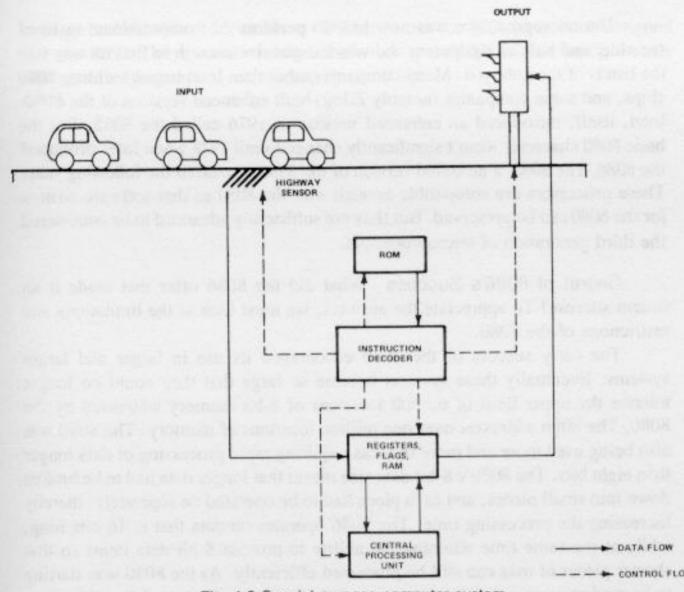

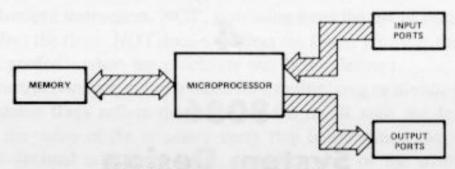

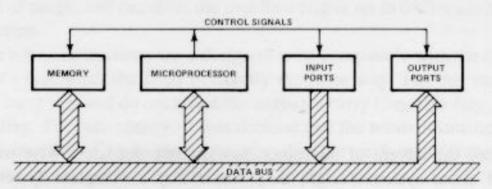

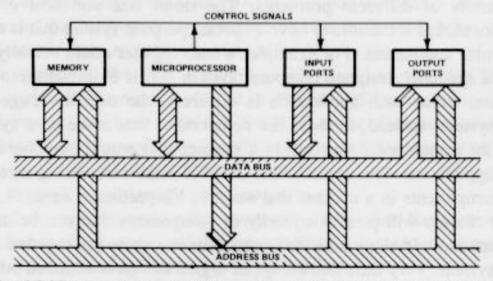

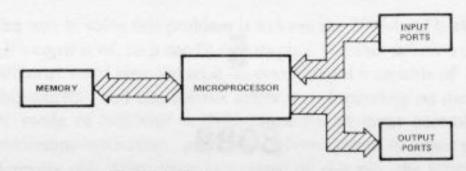

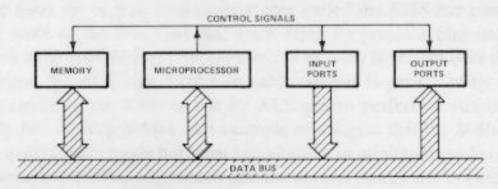

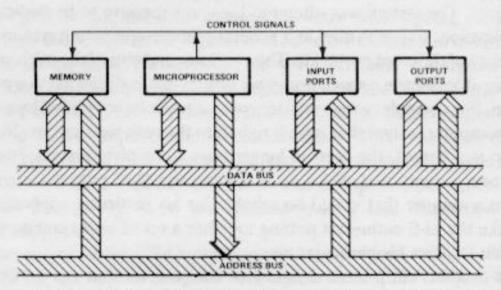

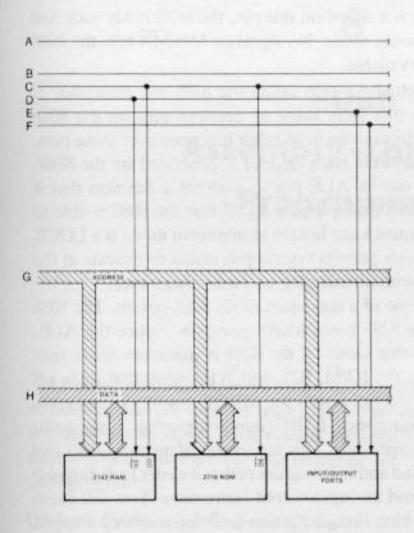

The basic units that make up a computing system are shown in Fig. 1.1. Figure 1.2 shows the same system except all the recognizable components are replaced by impersonal boxes. Let's examine the behavior of such a system by focusing on the function of each box.

The role of a computer is to obtain data from an input device, process the data, and deliver the final results to an output device. The particular processing to

Fig. 1.1 Primitive computing system.

Fig. 1.2 Modern general-purpose computing system.

be done is specified by a list of instructions called the *program*. The program is stored in the *program area*.

The operations of the computer are controlled by a device called a *control* unit. The control unit does the following three steps repeatedly:

- 1. Fetches an instruction from the program area

- Decodes the instruction to determine what operations are to be performed

- Executes the instruction by sending control signals to devices that perform the operations

The operations that are performed during instruction execution consist of moving data between devices and performing computations on data within a device. Computations are performed by the *arithmetic device*. The *data area* is used to supply inputs for the computations and to hold the intermediate results of the computations.

To see how all this ties together, let's analyze the execution of a particular instruction, namely an 'add' instruction. The control unit sends a control signal to the program area requesting the next instruction. The program area responds by sending an instruction to the control unit. The control unit then decodes the instruction and discovers it's an 'add' instruction. It then sends out control signals to (1) the data area telling it to move two values to the arithmetic device, (2) the arithmetic device telling it to add the two values it received, and (3) the data area telling it to receive the result of the addition.

The program area and the data area are similar in that both consist of memory in which information is stored. However, there is a big difference in the kind of information each area holds. The data area holds intermediate results, which are frequently changed during the execution of the program. The program area holds the program, which usually doesn't change while it is being executed. (Programs that modify themselves have fallen from favor in recent years.) In some systems the program is actually "engraved" into the memory so it can no longer be changed; it can only be read. Memories having this property are called read-only memories (ROM for short). A ROM would obviously be unsuitable for use in the data area. The data area consists of readable-writable memory that came to be called RAM by accident; it should have been called RWM. (RAM stands for random access memory, which unfortunately is not a very descriptive title.)

A memory is a collection of sequential *locations*, each having a unique address. Each location contains a sequence of bits (short for binary digits). These bits are the contents of the location. Each bit is either 0 or 1. More will be said about binary digits later in this chapter.

The data area consists of registers and flags in addition to memory. Like memory, the registers are also used to hold intermediate results. It's usually easier and faster to access values in registers than in memory. The computer uses the flags as indicators to keep track of what's going on. There are two kinds of flags—those that record information about the results generated by previously executed instructions (status flags) and those that control the operations of the computer (control flags). An example of a status flag is a flag that indicates a result is too big for the computer to handle. An example of a control flag is a flag that tells the computer to execute instructions at a slower rate, such as one per hour.

Another device in a computing system is a *port*. A port is the door through which information passes when coming from or going to an input or output device. For the sake of simplicity, ports were not shown in Figs. 1.1 and 1.2.

#### **Data Formats**

The contents of a memory location can represent either an instruction in the program or a piece of data. The ways instructions are stored—as a sequence of bits in a location—are called the *instruction formats* and may vary from one computer to another. The instruction formats of the 8086 are presented in Chap.

3. The data formats used in the 8086 are described here.

Data processed by a computer can be either numeric (numbers) or nonnumeric (characters). A payroll program might make extensive use of numeric data, whereas a text-editing program would be concerned with non-numeric data. The format used for storing non-numeric data is known as ASCII.

Number Systems We are accustomed to representing numbers as a sequence of decimal digits, such as 365. This is interpreted as 3 hundreds, 6 tens, and 5 ones. It is sometimes called a base-10 representation. It's no accident that we have ten fingers, and we use a base-10 representation for our numbers. Computers don't have fingers; they count with voltages. For reliability, they use

Table 1.1 Hexadecimal Representation

|                    | Group of Four Bits | Hexadecimal Digit | Value    |

|--------------------|--------------------|-------------------|----------|

| on similar di essa | 0000               | 0                 | zero     |

|                    | 0001               | 1                 | one      |

|                    | 0010               | 2                 | two      |

|                    | 0011               | 3                 | three    |

|                    | 0100               | 4                 | four     |

|                    | 0101               | 5                 | five     |

|                    | 0110               | 6                 | six      |

|                    | 0111               | 7                 | seven    |

|                    | 1000               | 8                 | eight    |

|                    | 1001               | 9                 | nine     |

|                    | 1010               | A                 | ten      |

|                    | 1011               | В                 | eleven   |

|                    | 1100               | C                 | twelve   |

|                    | 1101               | D                 | thirteen |

|                    | 1110               | E                 | fourteen |

|                    | 1111               | F                 | fifteen  |

only two voltage levels. They either have a voltage or they don't, and it's pretty difficult (though not impossible) to confuse the two situations. So it follows that computers want to represent numbers as a sequence of binary digits (bits), such as 11010. This is the base-2 representation of 1 sixteen, 1 eight, 0 fours, 1 two, and 0 ones. Binary numbers can be added, subtracted, multiplied, and divided directly (no need to convert them to decimal numbers first) as long as we remember that 1 plus 1 is 10 (1 two and 0 ones) and not 2. For example:

| 1001   | binary representation of nine     |

|--------|-----------------------------------|

| + 0101 | binary representation of five     |

| 1110   | binary representation of fourteen |

We tend to get confused with long sequences of binary digits, although computers aren't perturbed the least bit. For example, 10110101 is the binary representation for one hundred eighty-one. To make things simpler, we have devised a scheme of compressing long sequences of binary digits by grouping the bits four at a time. Each group of four is represented by a single character, as shown in Table 1.1. Thus 10110101 is abbreviated to B5. This is called a hexadecimal number and is exactly the number system we would have used if we had been born with 16 fingers.

Signed Numbers The binary notation is perfect for describing positive numbers and zero. But when we want to allow for negative numbers, we need to have an additional mechanism to indicate the sign of the number. The simplest way to do this is to use the most significant (leftmost) bit of the number to indicate the sign. For example:

| 0000 0100 | would be +4   |

|-----------|---------------|

| 1000 0100 | would be -4   |

| 0111 1111 | would be +127 |

| 1111 1111 | would be -127 |

Such a representation is called sign-magnitude representation and has one serious drawback: it requires a new set of arithmetic rules. This becomes obvious when we try to use binary arithmetic to subtract +1 from 0 and expect to get -1.

If we want to use the same binary arithmetic on signed numbers that we used on unsigned numbers, we need a signed-number representation in which  $1111\ 1111$  represents -1, not -127. Furthermore, subtracting +1 from -1 should give -2. Let's perform this subtraction to see what -2 should look like.

| 1111 1111   | here's -1        |

|-------------|------------------|

| - 0000 0001 | subtract +1      |

| 1111 1110   | and call this -2 |

So it seems that we should represent positive and negative numbers as follows:

| plus three  |

|-------------|

| plus two    |

| plus one    |

| zero        |

| minus one   |

| minus two   |

| minus three |

|             |

This is called a *two's complement* representation, and it has the property that binary additions and subtractions will give the correct two's complement result. For example:

| 0000 0011   | +3 in two's complement |

|-------------|------------------------|

| + 1111 1110 | -2 in two's complement |

| 0000 0001   | +1 in two's complement |

It also has the property that the most significant bit of every non-negative (positive or zero) number is 0 and of every negative number is 1. Thus, just like in

sign-magnitude representation, this bit serves as a sign bit. Properties of signed numbers are explored in more detail in Chap. 3.

The sign of a two's complement number can be changed by changing the value of each bit and adding +1. For example, we can obtain the two's complement representation of -3 from the two's complement representation of +3 as follows:

| 0000 0011   | +3 in two's complement   |

|-------------|--------------------------|

| 1111 1100   | +3 with each bit changed |

| + 0000 0001 | +1 in two's complement   |

| 1111 1101   | -3 in two's complement   |

There is one precaution to note about two's complement numbers. If an 8-bit two's complement number is to be extended to 16 bits (so that it can be added to a 16-bit two's complement number, for example), some thought must be given as to what goes into the additional eight bits.

Suppose we wanted to add  $0000\ 0001\ (+1\ in\ two's\ complement)$  to  $0000\ 0000\ 0001\ (+3\ in\ two's\ complement)$ . In this case there's no doubt that we would simply append eight 0's on the left side of the +1 and then add:

| 0000 0000 0000 0011   | (+3 in two's complement) |

|-----------------------|--------------------------|

| + 0000 0000 0000 0001 | (+1 in two's complement) |

| 0000 0000 0000 0100   | (+4 in two's complement) |

However, if we wanted to add 1111 1111 (-1 in two's complement) to 0000 0000 0000 0011 (+3 in two's complement), we must append eight 1's to the left side of -1 (appending 0's would make it a positive number). The addition is then:

| 0000 0000 0000 0011   | (+3 in two's complement) |

|-----------------------|--------------------------|

| + 1111 1111 1111 1111 | (-1 in two's complement) |

| 0000 0000 0000 0010   | (+2 in two's complement) |

Thus the extension of an 8-bit number to a 16-bit number looks like this:

| Value | 8-bit Representation | 16-bit Representation |

|-------|----------------------|-----------------------|

| +1    | 0000 0001            | 0000 0000 0000 0001   |

| -1    | 1111 1111            | 1111 1111 1111 1111   |

The rule for extending a two's complement number is to append additional bits on the left side of the number with each such appended bit having the same value as the original sign bit. This process is called sign extending.

Characters Characters can be represented as a sequence of bits. As a minimum we need to be able to represent 26 letters and 10 digits for a total of 36 characters. But it also would be nice to be able to distinguish between upper case and lower case letters (another 26 characters) and to be able to represent some special characters (+ and \* for example). So now we have over 64 characters and

thus need at least seven bits to represent a single character (the largest value that a 6-bit number can have is only 64). A commonly used 7-bit encoding is called ASCII (American Standard Code for Information Interchange) and is shown in Appendix C. An 8-bit memory location is called a byte of memory and is conveniently used for the storage of an ASCII-encoded character (the eighth bit is sometimes used as a check on the validity of the other seven).

#### Stacks

A stack is a concept that is frequently found in microprocessors as well as in larger machines. Other names for stacks are "pushdown lists" or "last-in-first-out queues." These names are intended to convey the image of a device for stacking cafeteria trays. When a new tray is placed on top of the stack of trays, it pushes all trays beneath it down one level. When the top tray is removed from the stack, all trays pop up one level. The last tray placed on the stack will be the first tray to be removed.

To understand what all this has to do with computers, we have to look at subroutines. Subroutines (sometimes called procedures) are parts of a program that are called upon to perform specific tasks. This provides a means of subdividing the total problem to be solved into smaller and simpler parts. A subroutine itself might call upon other subroutines to further subdivide the work. After a subroutine finishes its task, it returns control back to the routine that called upon it. The result is a sequence of subroutines, each calling upon other subroutines, until the last subroutine called upon decides to return. In other words, the last subroutine called will be the first subroutine to return.

When a subroutine is called upon, there is a certain amount of information that must be saved. This might include the current contents of some of the registers and the current settings of the flags. It certainly includes the address in the calling routine to which the subroutine will eventually return control. When the subroutine completes its task, it will retrieve this saved information so that it can restore the contents of the affected registers, set the flags to their original settings, and use the "return address" to return control to the appropriate instruction. But since the last subroutine called is the first subroutine to return, the last piece of information saved must be the first to be retrieved. Thus the information must be stacked like cafeteria trays.

So far we have described how a stack behaves and why a stack would be a useful thing in a computer. Now let's see how a computer stack can be implemented. Since the stack has to hold information, it must be some kind of memory. Actually any portion of the available memory (other than the read-only memory) can be used as a stack. All that is needed is a pointer to the last piece of information that was placed in the stack portion of memory. This pointer is often called the *stack pointer*, and the information it points at is usually called the *top of the stack*. When a new piece of information is placed on the stack (a process referred to as *pushing*), the stack pointer is updated so that it points to the next memory location, and the information is placed in that location. When a piece of memory is retrieved from the stack (a process referred to as *popping*), the

information is retrieved from the memory location that the stack pointer is pointing at, and the stack pointer is again updated—but this time in the opposite direction.

#### 8086 Memory Utilization (A Sneak Preview)

The preceding sections have illustrated that memory may be used to hold the program (code), to store data (numeric and character), and as a stack. Thus it is not surprising that the 8086 actually separates its memory into code segments, data segments, and stack segments. These segments of memory are discussed in Chap. 2.

#### The Microcomputer Story

Now that we've summarized the basic concepts of a computer, let's take a look at the history of computers and see how they evolved into microcomputers.

From Big Computers to Microcomputers In the 1950s all electronic devices (radios and televisions, as well as computers) were built of bulky vacuum-tube devices. Computers of that vintage are sometimes referred to as first-generation computers. Examples are IBM's 650 and 704. These computers were housed in large rooms containing several racks of electronic equipment. By the end of the decade, transistors and other solid-state devices began to replace vacuum tubes. Computers using this technology are called second-generation computers (the IBM 7090 and the Burroughs B5500, for example).

In the 1960s many discrete electronic components (resistors, capacitors, transistors, etc.) were combined into one single complex electronic component called an *integrated-circuit* (*IC* for short). The IC is fabricated on a wafer of silicon smaller than a postage stamp. It is mounted on a centipede-like structure that can be plugged into a system. This pluggable integrated-circuit became known as a *chip*. Computers built out of IC chips are the third-generation computers (the IBM 360, the GE 635, and the Burroughs B6700). But the integrated-circuit technology continued to advance, and by the early 1970s many of the components in Fig. 1.2 could be put together onto a single chip (Intel's 4004 and 8008). This led to the coining of the term *computer-on-a-chip*.

By this time, not only had the size of computers been drastically reduced, but so had the price. The vacuum-tube computers were priced in the millions of dollars. Computers-on-a-chip were initially priced around \$300, and within a few years competition drove that price down to less than \$10.

Computers-on-a-chip are called microcomputers or microprocessors. Although the terms are sometimes used interchangeably, there is a difference. A microprocessor is a single chip. It usually consists of a control unit, an arithmetic and logical unit, registers, flags, and interfaces to both memory and input/output devices. Program and data memory, as well as input/output devices, are usually not on the chip. A microcomputer is an entire computer system consisting of a microprocessor chip, memory chips, and input/output devices. Sometimes the

Fig. 1.3 Special-purpose computer system

entire computer system is contained on one chip (Intel's 8048). This is called a single-chip microcomputer.

As computers became small and inexpensive, it became economical to build them into special-purpose systems such as cash registers, calculators, and typewriters. An example of a computer built into a traffic light is shown in Fig. 1.3. It is not surprising that microprocessors are frequently found in such special-purpose control applications.

From 8008 to 8086 The microprocessor era started with the introduction of Intel's 4004 and 8008 processors in 1971. This was the first generation of microprocessors. Both of these chips were designed for specialized applications—the 4004 in a calculator and the 8008 in a computer terminal. These microprocessors were somewhat of a novelty and not taken seriously. But by 1974 when the 8008 matured into the 8080 (the second-generation microprocessor), the computer industry began to take notice. The 8080 was the first microprocessor deliberately designed to be useful in a great variety of applications. It quickly became the "standard" microprocessor.

The microprocessor was now able to perform the computational tasks of the older and bulkier equipment and was inexpensive enough to find its way into the hands of the hobbyist. Many companies other than Intel began building 8080 chips, and some companies (notably Zilog) built enhanced versions of the 8080. Intel, itself, introduced an enhanced version in 1976 called the 8085. But the basic 8080 character wasn't significantly changed until 1978 when Intel produced the 8086. The 8088, a modified version of the 8086, appeared the following year. These processors are compatible enough with the 8080 so that software written for the 8080 can be preserved. But they are sufficiently advanced to be considered the third generation of microprocessors.

Secret of 8086's Success What did the 8086 offer that made it an instant success? To appreciate the answers, we must look at the limitations and restrictions of the 8080.

The early success of the 8080 encouraged its use in larger and larger systems. Eventually these systems became so large that they could no longer tolerate the upper limit of 65,000 locations of 8-bit memory addressed by the 8080. The 8086 addresses over one million locations of memory. The 8080 was also being used more and more in areas requiring rapid processing of data longer than eight bits. The 8080's 8-bit data size meant that longer data had to be broken down into small pieces, and each piece had to be operated on separately, thereby increasing the processing time. The 8086 operates on data that is 16 bits long, while at the same time retaining the ability to process 8-bit data items so that shorter pieces of data can still be processed efficiently. As the 8080 was starting to be used as a general-purpose computer, the lack of multiply and divide instructions and the lack of operations on signed numbers were making it cumbersome to use. The 8086 provides these previously missing arithmetic facilities. More and more 8080 programs were being written in a high-level language and then translated into a language understood by the 8080. The means by which the 8080 could address its data did little to provide for the creation of efficient 8080 code from programs written in a high-level language. The addressing modes of the 8086 were designed to accommodate high-level-language processing. A fair number of applications found the 8080 pitifully trying to juggle strings of data, a task for which it was ill-prepared. The 8086 was designed to process data strings efficiently. And, finally, as systems became more and more complex, no single processor could be expected to perform all the functions of the system. But the 8080 never learned how to cooperate with other processors. The 8086, on the other hand, was designed to be used in a multiprocessor environment.

Secret of 8088's Success What did the 8088 offer that also made it a success? For one thing, it contained all the advanced features found in the 8086. But the amount of data transferred between the 8086 processor and memory at one time is twice as much as the 8080 is able to transfer. Although being able to transfer more data at a time is usually a desirable feature (that's why the 8086

was given this ability), it makes it difficult to use the 8086 in systems designed for the 8080. The amount of data transferred by the 8088 at one time is exactly the same as the amount transferred by the 8080.

# 8086 Machine Organization

#### Overview

One way to describe a computer is to describe the functional components that make up that computer. A description of these components and the interaction between them is sometimes referred to as the architecture of the computer. It is concerned with such things as how many registers are in the computer, what functions the registers serve, how much memory can be connected, how the memory is addressed, and what sort of input/output facilities are available.

The 8086 is a single integrated-circuit chip containing most of the components that make up a computer. The circuitry that controls all the functions of the computer is contained on that chip. Also contained on the chip are all of the registers and flags. The memory and input/output ports are not contained on the chip but can be easily connected to the chip to form a computer. The collection of all those things on the chip is sometimes referred to as the *processor*.

If we had to summarize the architecture of the 8086 in one paragraph, it would be as follows: "The 8086 has four sets of registers. One set contains general registers that are used to hold intermediate results. The second set contains pointer and index registers that are used to locate information within a specified portion of memory. The third set contains segment registers that are used to specify these portions of memory. And the fourth set contains the instruction pointer. There are also nine flags in the 8086. These flags are used to record the state of the processor and to control its operation. The 8086 can access up to 1,000,000 bytes of memory and up to 65,000 input or output ports." The first half of this chapter will elaborate on these features.

Typical computer instructions involve locating designated operands (data to be processed), performing an operation on the values of these operands, and storing the result back into a designated result location. The locations of the operands and of the result can be either in memory or in a register as designated by the instruction. The facilities available for designating these locations are referred to as the operand-addressing modes of the computer. The operand-

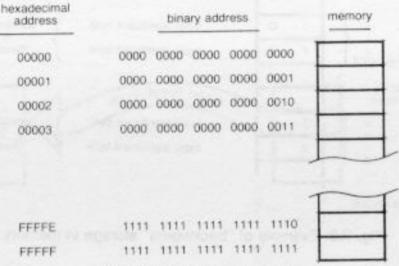

Fig. 2.1 Memory addresses

Fig. 2.2 Examples of words in memory.

addressing modes of the 8086 will be described in the second half of this chapter. The actual instructions that operate on the designated operands are described in Chap. 3.

#### Memory Structure

Any two consecutive bytes in memory are defined as a word. Each byte in a word has a byte address, and the smaller of these two addresses is used as the address of the word. Examples of words are shown in Fig. 2.2

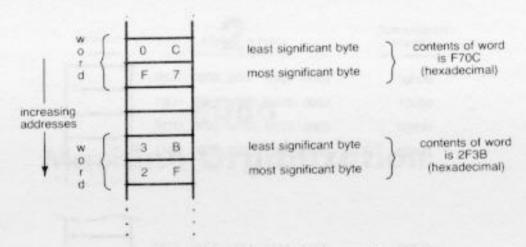

Fig. 2.3 Example of "backwords" storage in memory.

A word contains 16 bits. The byte with the higher memory address contains the eight most significant bits of the word, and the byte with the lower memory address contains the eight least significant bits. On first reading, this seems very natural. Of course the most significant byte should have the higher memory address. But then when you consider that memory is a sequence of bytes starting at the lowest address and going toward the highest address, it becomes apparent that the 8086 stores its words backwards (perhaps they should be called backwords). This is illustrated in Fig. 2.3.

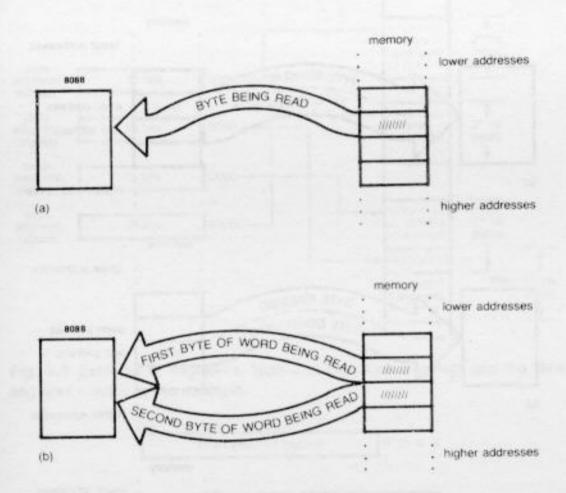

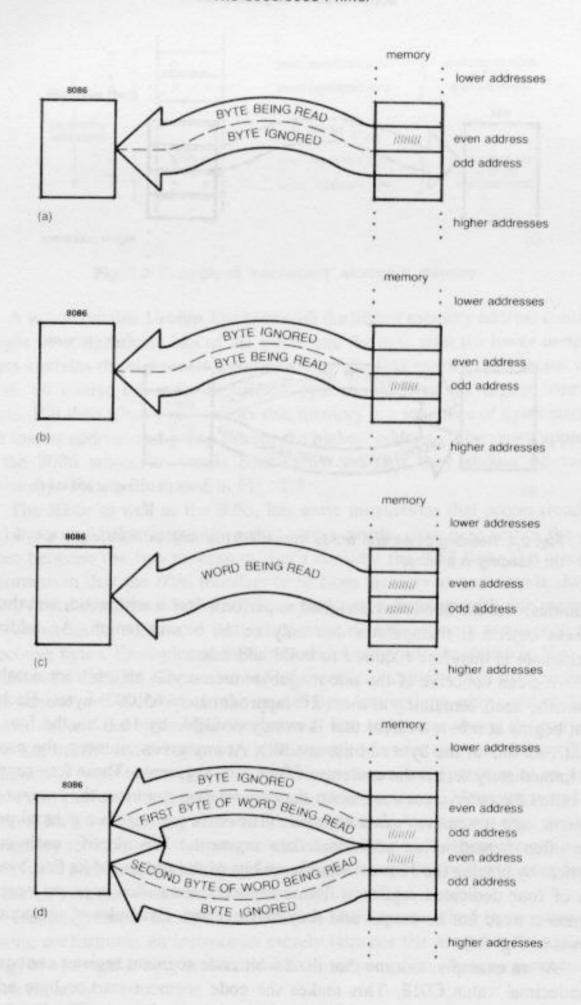

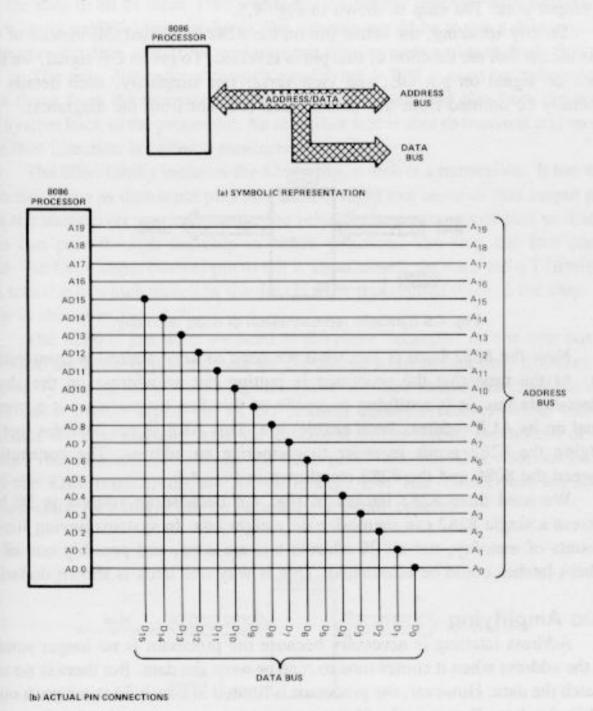

The 8086, as well as the 8088, has some instructions that access (read or write) bytes and other instructions that access words. Now here comes the difference between the two processors. Let's consider the 8088 first. The amount of information that the 8088 transfers to or from memory at one time is always 8 bits. A byte instruction in the 8088 can perform its function with one memory access, whereas an 8088 word instruction must do two memory accesses to two consecutive bytes. Examples of 8088 byte and word reads are shown in Fig. 2.4.

Now for the 8086. The amount of information it transfers to or from memory at one time is always 16 bits. In the case of byte instructions, only eight of those bits are used and the other eight are ignored. The 16 bits are always the contents of two consecutive bytes in memory starting with a byte at an even address. That means that a word instruction that reads or writes a word starting at an even address can perform its function with one memory access. However, word instructions for words starting at odd addresses must do more work; they must do two memory accesses to two consecutive even-address words, ignore the unwanted half of each, and do some byte juggling with the remaining halves. Examples of the various byte and word reads are shown in Fig. 2.5.

The program in the 8086 (or 8088) is oblivious to all of these memoryaccessing contortions; an instruction merely requests the accessing (reading or writing) of a particular byte or word, and the processor does whatever is necessary to perform such an access.

#### Memory Segmentation

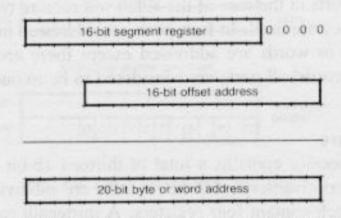

Since the 8086 can address up to 220 bytes of memory, it would seem that, within the 8086 processor, byte and word addresses must be represented as 20-bit

Fig. 2.4 Reading bytes and words from 8088 memory. (a) Reading in a byte. (b) Reading in a word.

quantities. But the 8086 was designed to perform 16-bit arithmetic, and thus the address objects it manipulates can only be 16 bits in length. An additional mechanism is therefore required to build addresses.

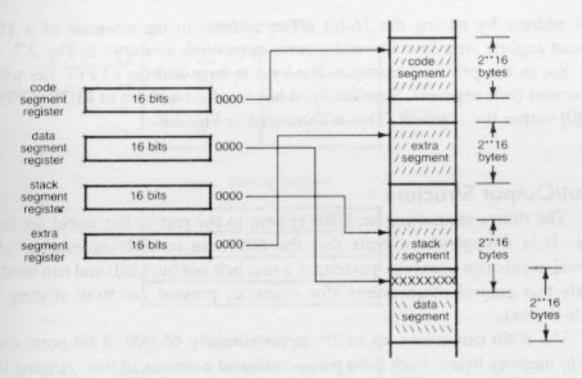

We can conceive of the one megabyte memory as an arbitrary number of segments, each containing at most 216 (approximately 65,000) bytes. Each segment begins at a byte address that is evenly divisible by 16 (i.e., the four least significant bits of the byte address are '0'). At any given moment, the program can immediately access the contents of four such segments. These four segments are called the current code segment, the current data segment, the current stack segment, and the current extra segment. (The extra segment is a general-pupose area often treated as an additional data segment.) We identify each current segment by placing the 16 most significant bits of the address of its first byte into one of four dedicated registers. These registers are called segment registers. Segments need not be unique and they may overlap. Examples of segments are shown in Fig. 2.6.

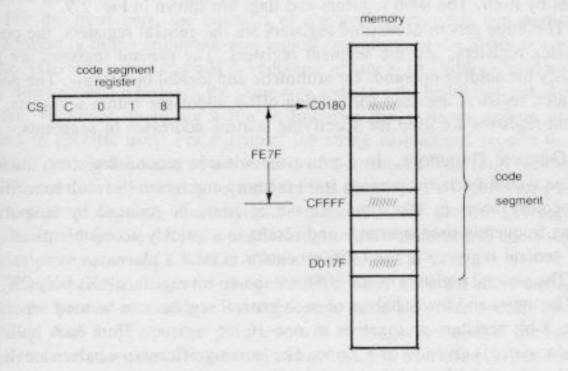

As an example, assume that the 16-bit code segment register contains the hexadecimal value C018. This makes the code segment start at byte address C0180 and extend for a total of 2<sup>16</sup> (10000 hexadecimal) bytes. The last byte in the code segment is therefore at byte address D017F.

We refer to bytes or words within a segment by using a 16-bit offset address within the 216 byte segment. The processor constructs the 20-bit byte or

Fig. 2.5 Reading bytes and words from 8086 memory at even and odd addresses. (a) Reading in even-addressed byte. (b) Reading in odd-addressed byte. (c) Reading in even-addressed word. (d) Reading in odd-addressed word requires two memory accesses.

Fig. 2.6 Example of segments. Note that the stack segment and the data segment overlap in this example.

Fig. 2.7 Constructing byte or word addresses.

Fig. 2.8 Example of constructing byte address (see text).

word address by adding the 16-bit offset address to the contents of a 16-bit segment register with four low-order zeros appended, as shown in Fig. 2.7.

So, in the previous example, the byte at byte-address CFFFF lies within the current code segment. Specifically, it has an offset address of FE7F (CFFFF-C0180) within the segment. This is illustrated in Fig. 2.8.

#### Input/Output Structure

The things connecting an 8086 system to the rest of the world are called ports. It is through these ports that the 8086 can receive information about external events (for example, passenger's seat belt not buckled) and can send out signals that control other events (for example, prevent car from starting and heckle driver).

The 8086 can access up to 2<sup>16</sup> (approximately 65,000) 8-bit ports analogous to memory bytes. Each 8-bit port is assigned a unique address ranging from 0 to 2<sup>16</sup>—1. Any two consecutive 8-bit ports can be treated as a 16-bit port analogous to memory words; and, like memory words, 16-bit ports at odd addresses (all 16-bit ports in the case of the 8088) will require two accesses instead of one each time they are used. In fact, ports are addressed in the same manner that memory bytes or words are addressed except there are no port segment registers. In other words, all ports are considered to be in one segment.

#### Register Structure

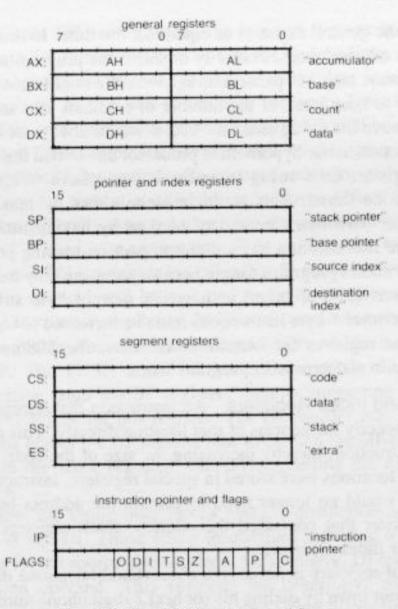

The 8086 processor contains a total of thirteen 16-bit registers and nine 1-bit flags. For descriptive purposes, the registers are subdivided into four sets. Three of the sets each contain four registers. A thirteenth register, namely the instruction pointer, is not directly accessible to the programmer and is therefore in a set by itself. The 8086 registers and flags are shown in Fig. 2.9.

The three sets of accessible registers are the general registers, the pointer and index registers, and the segment registers. The general registers are used primarily for holding operands for arithmetic and logical operations. The pointer and index registers are used for holding offset addresses within segments. The segment registers are used for specifying starting addresses of segments.

General Registers In a processor without general registers, each instruction would fetch its operands from memory and return its result to memory. But memory accesses take time. This time could be reduced by temporarily keeping frequently used operands and results in a quickly accessible place. The set of general registers in the 8086 processor is such a place.

The general registers of the 8086 are the 16-bit registers AX, BX, CX, and DX. The upper and lower halves of each general register can be used separately as two 8-bit registers or together as one 16-bit register. Thus each half of a general register is given its own name. The least significant low halves are named AL, BL, CL, and DL, and the most significant high halves are named AH, BH,

Fig. 2.9 The 8086 registers and flags.

CH, and DH. The dual nature of these registers permits them to handle both byte and word quantities with equal ease.

For the most part, the contents of the general registers can participate interchangeably in the arithmetic and logical operations of the 8086. For example, the ADD instruction can add the contents of any 8- or 16-bit general register to any other general register of the same size and store the result into either of the registers. However, there are a few instructions that dedicate certain general registers to specific uses. For example, the string instructions require the CX register to contain the count of the number of elements in the string. Neither the AX, BX, nor DX register may be used for this purpose. This specialized use of the CX register suggests the descriptive name COUNT for the CX register. Specialized uses for the AX, BX, and DX registers (to be described later) suggest the descriptive names ACCUMULATOR, BASE, and DATA.

These specialized uses of the general registers have the disadvantage of making the processor harder to learn because there are more special rules to memorize. And it appears that programs will be longer because of the need to move data from one general register to another prior to executing certain instructions. However, let's consider how we would write a program for a processor

that treated all the general registers as equals all the time. In order to keep track of where things are, we would probably organize the program so that particular kinds of data always reside in particular registers. We might choose to always use the CX register to keep track of the number of elements in a string. We would never have to move the string size into CX; it would always be there. But since the string instruction in our hypothetical processor can obtain the string size from any general register, each string instruction would have to specify where its string size is to be found. This could be done either by making each string instruction longer (two bytes instead of one) or by having more 1-byte string instructions. The first solution has a direct impact on making programs longer. The second also makes programs longer because there are only a small number of 1-byte instructions (256 of them) and having more 1-byte string instructions means that some other 1-byte instructions must be increased to two bytes. So, by having dedicated registers for certain instructions, the 8086 architecture has actually resulted in a decrease in program size.

Pointer and Index Registers An instruction that accesses a location in memory could specify the address of that location directly. This address takes up space in the instruction, thereby increasing the size of the code. If addresses of frequently used locations were stored in special registers, instructions that access these locations would no longer need to contain the address but could instead specify the register that contained the address. Such registers are sometimes called pointer or index registers.

This use of registers is not unlike abbreviated telephone dialing. You can call anyone in your town by dialing his (or her) 7-digit phone number. Or, if your telephone company provides this service, you can enter some frequently called phone numbers into a set of 'registers.' Then you can call these selected people by dialing only the one or two digits that specify the register.

The pointer and index registers of the 8086 consist of the 16-bit registers SP, BP, SI, and DI. These registers generally contain offset addresses for addressing within a segment. For example, an ADD instruction could specify that one of its operands is located in the current data segment of memory at an offset contained in a particular pointer or index register (say SI).

Pointer and index registers serve another (and perhaps more important) function besides reducing the size of instructions; they permit instructions to access locations whose offset addresses are the result of previous computations performed while the program is running. It is often necessary to perform such computations in order to establish the offset address of variables, especially in high-level language programs. These computations could be performed in a general register and the result moved to a pointer or index register to be used as an offset. Elimination of such moves would result in shorter programs. For this reason, the values contained in pointer and index registers are permitted to participate in arithmetic and logical operations along with the 16-bit general registers. Thus the ADD instruction mentioned above could specify that its other operand is the contents of the DI register.

There are some differences among the registers that result in dividing this set of registers into the pointer registers SP and BP, and the index registers SI and DI. The pointer registers are intended to provide convenient access to data in the current stack segment as opposed to the data segment. This use of the stack segment as a "data area" has certain advantages (which will be discussed at the end of this chapter) for the implementation of high-level languages. Thus, unless a segment is specifically designated, offsets contained in the pointer registers are assumed to refer to the current stack segment, whereas offsets contained in the index registers are generally assumed to refer to the current data segment. (If the word "generally" is used, you can bet there'll be an exception mentioned soon.) For example, if an ADD instruction specifies that SI contains the offset of one of its operands, that operand will be assumed to be in the current data segment unless the ADD instruction explicitly designates some other segment.

There are some instructions that distinguish between the two pointer registers SP and BP. The PUSH and POP instructions obtain the offset for the top-of-stack location from the SP register, thereby suggesting the descriptive name STACK POINTER for this register. The BP register may not be used for this purpose. This leaves the BP register free to contain the offset of the "base" of a data area in the stack segment, thereby suggesting the descriptive name BASE POINTER.

Furthermore, the string instructions make a distinction between the two index registers SI and DI. Those string instructions requiring a source operand obtain the offset for the source operand from SI; similarly, DI contains the offset of the destination operand. This suggests the descriptive names SOURCE INDEX and DESTINATION INDEX. For those string instructions, the roles of SI and DI may not be interchanged. As an example, the string-move instruction will move the string located in the current data segment starting at the offset contained in SI and relocate it to the current extra segment (there's the exception you were promised) at the offset contained in DI; the SI and DI registers are not explicitly mentioned by the string-move instruction. (Incidentally, the destination string is in the extra segment instead of in the data segment so that each string would have a segment of its own and could be up to 2<sup>16</sup> bytes long.)

Segment Registers You will recall that the 8086 has a one megabyte memory, but addresses contained in instructions and in pointer and index registers are only 16 bits long. These addresses cannot be addresses in the one megabyte memory but must be address offsets into some particular 65,000 byte segment. But which one?

The segment registers of the 8086 are the 16-bit registers CS, DS, SS, and ES. These registers are used to identify the four segments that are currently addressable. Each register identifies a particular current segment, and they cannot be used interchangeably: CS identifies the current code segment, DS the current data segment, SS the current stack segment, and ES the current extra segment.

OK. An instruction specifies an offset into a segment, and the segment registers specify the four segments we could use. Which one do we select? The answer depends on how the offset is to be used. An offset might be specifying the next instruction to be executed, or it might be specifying an operand for an instruction.

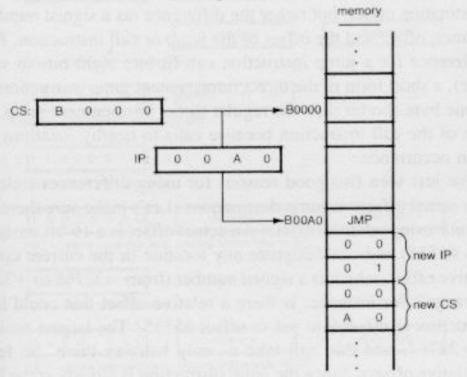

All instruction fetches are taken from the current code segment. So we need a register that contains the offset in the current code segment of the next instruction to be executed. This is the purpose of IP, the INSTRUCTION POINTER. For example, if CS contains hexadecimal 1FF7 and IP contains hexadecimal 003A, then the next instruction fetched would come from memory location 1FFAA because:

1FF70 code segment start address

+ 003A offset contained in IP

1FFAA memory address of next instruction

(You will recall from Fig. 2.6 that the hexadecimal digit "0" is appended to the value in the segment register when constructing memory addresses.)

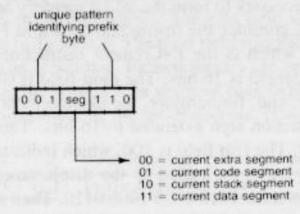

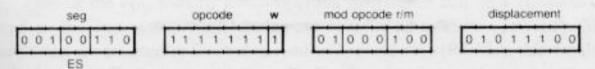

The segment for operand fetches can generally be designated by preceding the instruction with a special 1-byte prefix. This prefix specifies from which of the four current segments the operand is to be fetched. In the absence of such a prefix (the usual case), the operand is taken from the current data segment unless (1) the offset address was calculated from the contents of a pointer register, in which case the current stack segment is used; or (2) the operand is the destination operand of a string instruction, in which case the current extra segment is used. (The reasons for these two exceptions were mentioned in the previous section.)

As an example, consider an ADD instruction that has one of its operands in the data segment and at the offset contained in SI. The instruction would specify SI in its operand field but would make no mention of DS. When executing the instruction, the processor would know to use the contents of DS along with the contents of SI in order to locate the operand. Next, consider an ADD instruction for which the operand is in the code segment (as might be the case with constants in ROM) and at the offset contained in SI. This ADD instruction would, as before, specify SI in its operand field; but, in addition, the instruction would be preceded by a prefix byte specifying CS.

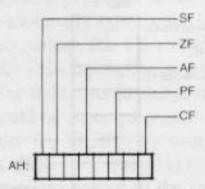

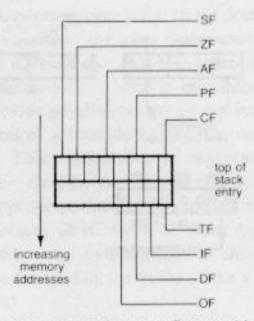

Flags The 8086 contains nine flags that are used to record processor status information (status flags) or to control processor operations (control flags). The status flags are generally set after the execution of arithmetic or logical instructions to reflect certain properties of the results of such operations. These flags are the carry flag (CF), indicating if the instruction generated a carry out of the most significant bit; the auxiliary carry flag (AF), indicating if the instruction generated a carry out of the four least significant bits; the overflow flag (OF), indicating if the instruction execution generated a signed result that is out of range; the zero flag (ZF), indicating if the instruction generated a zero result; the

sign flag (SF), indicating if the instruction generated a negative result; and the parity flag (PF), indicating if the instruction generated a result having an even number of "1" bits.

The control flags are the direction flag (DF), which controls the direction of the string manipulation instructions; the interrupt-enable flag (IF), which enables or disables external interrupts; and the trap flag (TF), which puts the processor into a single-step mode for program debugging.

More details will be given on each of these flags throughout Chap. 3, and

the final section of that chapter summarizes the behavior of the flags.

#### Instruction Operands and Operand-Addressing Modes

Instructions in the 8086 usually perform operations on one or two operands. For example, the ADD instruction adds the value contained in one operand to the value contained in a second operand and stores the result back into one of these operands. The INCrement instruction adds 1 to the value contained in the operand and stores this result back into the operand. The time has come to show how an instruction specifies its operands (more formally referred to as its operand-addressing modes).

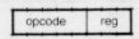

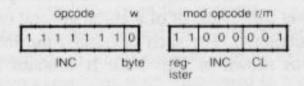

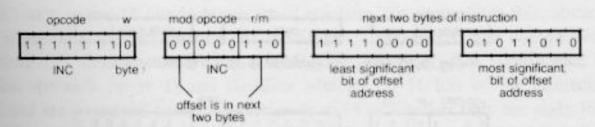

Single Operand Let's examine an instruction that specifies a single operand, such as the INCrement instruction. The most common uses of the INCrement instruction are to increment the contents of a pointer or index register (when computing offset addresses) or of a 16-bit general register (when performing arithmetic computations). For such operands, the instruction takes a very simple 1-byte form as shown in Fig. 2.10. It contains a 3-bit reg field that

Fig. 2.10 Single-operand instruction where operand is in a 16-bit register.

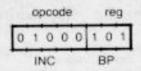

specifies one of the eight 16-bit registers (general, pointer, or index). The register encodings used in the **reg** field are shown in the first two columns of Table 2.1. The remaining five bits of the instruction identify the operation and are collectively referred to as the *opcode*. In the case of INCrement, the opcode is 01000. As an example, the instruction that increments the contents of the BP register is shown in Fig. 2.11. This operand-addressing mode is sometimes referred to as the *register-mode*. Table 2.2 summarizes all the operand-addressing modes. addressing modes.

Fig. 2.11 Instruction that increments contents of BP.

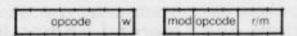

Fig. 2.12 Single-operand instruction where operand is in a register or memory.

memory. If the operand is in a register, the  $\mathbf{r/m}$  field specifies which register; if the operand is in memory, the  $\mathbf{r/m}$  field tells where in memory it is  $(\mathbf{r/m})$  stands for register or memory).

First consider the case where the operand is in a register ( $\mathbf{mod} = 11$ ). The register encodings used in the  $\mathbf{r/m}$  field are shown in Table 2.1. This is another instance of the register operand-addressing mode. As an example, the instruction that increments the contents of the CL register is shown in Fig. 2.13.

Fig. 2.13 Instruction that increments contents of CL.

Now consider the case where the operand is in memory (**mod** = 00, 01, or 10). This operand-addressing mode is sometimes referred to as *indirect memory addressing* because the operand is in memory but the offset is not specified directly. Instead, it is obtained by adding together a seemingly strange assortment of values. (The usefulness of such a mode will be justified in the next section.) The offset is the sum of up to three numbers: a 16-bit value (called a *displacement*) specified in the instruction, the contents of an index register (SI, DI, or none) specified in the instruction, and the contents of a base register (BX, BP, or none) specified in the instruction. The **r/m** field specifies the base and index register as shown in Table 2.3. The **mod** field specifies the displacement as shown in Table 2.4. The offset thus formed locates the operand within its segment. The operand is in the current data segment (unless the contents of pointer register BP were used in computing the offset address, in which case the operand

Fig. 2.14 An example of memory operand (see text).

Table 2.1 Register Encoding

|     | 16-bit Register | 8-bit Register |  |

|-----|-----------------|----------------|--|

| 000 | AX              | AL             |  |

| 001 | CX              | CL             |  |

| 010 | DX              | DL             |  |

| 011 | BX              | BL             |  |

| 100 | SP              | AH             |  |

| 101 | BP              | CH             |  |

| 110 | SI              | DH             |  |

| 111 | DI              | BH             |  |

Table 2.2 Operand Addressing Modes

IMMEDIATE REGISTER DIRECT MEMORY ADDRESSING INDIRECT MEMORY ADDRESSING

> base register index register

base register + index register base register + displacement

index register + displacement

base register + index register + displacement

Table 2.3 Base and Index Register Specified by r/m for Operands in Memory (mod ≠ 11)

|      | r/m Field | Base Register | Index Register |

|------|-----------|---------------|----------------|

| MESS | 000       | BX            | SI             |

|      | 001       | BX            | DI             |

|      | 010       | BP            | SI             |

|      | 011       | BP            | DI             |

|      | 100       | none          | SI             |

|      | 101       | none          | DI             |

|      | 110       | BP            | none           |

|      | 010001111 | BX            | none           |

If mod = 00 and r/m = 110, see note below Table 2.4.

is in the current stack segment). Still another addition, involving the contents of a segment register, is necessary to form the 20-bit memory address of the operand.

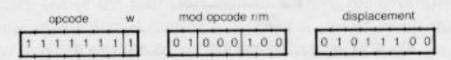

As an example, consider the instruction shown in Fig. 2.14. The opcode field is 1111111 000, which is the INCrement instruction. The w field is a 1, which indicates the operand is 16 bits. The mod field is 01, which indicates the operand is in memory; and, furthermore, the displacement is the contents of the next byte of the instruction sign extended to 16 bits. Thus the displacement is 0000 0000 0101 1100. The r/m field is 100, which indicates that the contents of the index register SI are to be added to the displacement to form the offset address. Assume SI contains 1010 0000 1000 0110. Then the offset address is as follows:

Table 2.4 Displacement as Specified by mod for Operands in Memory (mod ±11)

| Mod | Displacement                                                                                                                                                             | Comment                                    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 00  | zero (16 bits worth)                                                                                                                                                     |                                            |

| 01  | 8-bit contents of next byte<br>of instruction sign extended<br>to 16 bits                                                                                                | Instruction contains<br>an additional byte |

| 10  | 16-bit contents of next two<br>bytes of instruction (next byte<br>contains least significant<br>eight bits and byte after that<br>contains most significant eight bits). | Instruction contains two additional bytes  |

If mod = 00 and r/m = 110, then:

2. Instruction contains two additional bytes

Offset address is contained in those bytes (least significant eight bits precede most significant eight bits)

| 1010 0000 1000 0110   | contents of SI |

|-----------------------|----------------|

| + 0000 0000 0101 1100 | displacement   |

| 1010 0000 1110 0010   | offset address |

Since BP was not used in computing the offset address, the offset refers to the current data segment. Assume DS contains 1111 0000 1111 0000. Then the memory address of the operand is as follows:

| 1111 0000 1111 0000      | data segment   |

|--------------------------|----------------|

| + 1010 0000 1110 0010    | offset address |

| 1111 1010 1111 1110 0010 | memory address |

The operand is 16 bits wide (specified by the w field) so the operand is the contents of the bytes located at address 1111 1010 1111 1110 0010 and at address 1111 1010 1111 1110 0011 with the higher-addressed byte being the most significant.

Fig. 2.15 Segment-overriding prefix.

<sup>1.</sup> Tables 2.3 and 2.4 do not apply

The operand need not be restricted to the current data segment or stack segment. It can be fetched from any one of the four current segments by preceding the instruction with a 1-byte prefix denoting a segment register. This 1-byte prefix is shown in Fig. 2.15. As an example, Fig. 2.16 shows the same instruction as Fig. 2.14 except that now the operand is in the current extra segment.

Fig. 2.16 Example of using segment-overriding prefix (see text).

So far we have shown how to specify the offset of an operand in memory by going through a base and/or index register. But often we know exactly where the operand is, and we want to specify the offset directly in the instruction. This mode of operand addressing is called *direct memory addressing*. In this mode, the offset is contained in two bytes of the instruction (''backwords,'' of course). The remainder of the instruction must specify the opcode and the fact that the mode is direct memory addressing. It would be convenient to use a combination of the bits in the **mod** and  $\mathbf{r/m}$  fields to indicate this mode. Unfortunately, all the combinations have already been accounted for by the indirect memory-addressing mode and the register mode. But one of these combinations corresponded to an infrequently used indirect memory-addressing mode and so was chosen to correspond to direct memory addressing instead. This combination is  $\mathbf{mod} = 00$  and  $\mathbf{r/m} = 110$ . For example, the instruction which increments the byte at offset 0101 1010 1111 0000 in the current data segment is shown in Fig. 2.17.

The infrequently used mode that was lost to the direct memory-addressing mode is indirect through BP (no index register and no displacement). So now an instruction that forms its offset from just the BP register and a zero displacement will need to have **mod** = 01 and use one byte in the instruction to specify the zero displacement.

Fig. 2.17 Instruction that increments byte at offset 0101 1010 1111 0000 in current data segment.

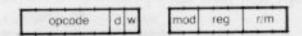

Two Operands Now that we've mastered the one-operand instruction, let's consider an instruction that has two operands such as ADD. As mentioned previously, ADD takes the value of one operand, adds it to the value of the other operand, and stores the result back in the location of either operand. If both

operands could be in memory, the instruction would need a **mod** field and an **r/m** field for each. To keep the instruction short, it was decided that at least one of the operands must be in a register. Now the instruction needs a **mod** and **r/m** field for one of the operands but only a **reg** field for the other. This is shown in Fig. 2.18.

Fig. 2.18 Typical two-operand instruction.

The two-operand instruction uses the **w** field to indicate if the operands are eight bits ( $\mathbf{w} = 0$ ) or 16 bits ( $\mathbf{w} = 1$ ). Also present is a new field not encountered before, namely the **d** field (**d** stands for destination). The **d** field specifies whether the result should be stored back into the operand specified by the **mod** field and  $\mathbf{r/m}$  field ( $\mathbf{d} = 0$ ) or into the operand specified by the **reg** field ( $\mathbf{d} = 1$ ). The operand into which the result is to be stored is called the *destination operand*, and the remaining operand is called the *source operand*.

As an example, consider the ADD instruction shown in Fig. 2.19. The opcode for ADD is 000000. The w field is 0, specifying that both operands are eight bits. The operand specified by the reg field is CH. The mod field is 11, specifying that the mod r/m operand is in a register, and the r/m field identifies the register as being BL. The d field specifies that the result is to be placed back into the operand specified by the reg field, namely CH. Thus the instruction will add the contents of register BL, the source operand, to the contents of register CH, the destination operand, and store the result back into CH.

Fig. 2.19 Example of two-operand instruction (see text).

Fig. 2.21 Example of immediate-operand instruction (see text).

|        | - |                |             |               |

|--------|---|----------------|-------------|---------------|

| opcode | W | mod opcode r/m | data        | data if w = 1 |

|        | - |                | <del></del> |               |

Fig. 2.22 Immediate-operand instruction using mod and r/m fields.

Fig. 2.23 Example of immediate-operand instruction using mod and r/m fields (see text).

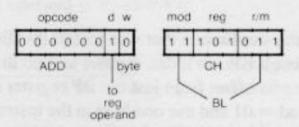

One of the operands of a two-operand instruction can be a constant contained in the instruction itself (referred to as an *immediate operand*). Since instructions are frequently located in read-only memories (ROMs), this would be an ideal place to keep constant operands. But forget about trying to store a result back into such an operand. The memory won't allow it.

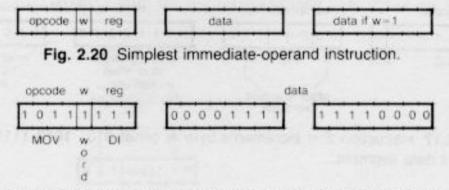

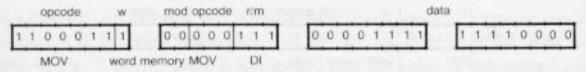

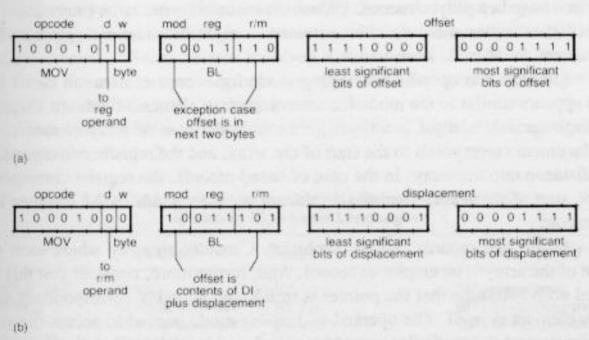

An instruction that can specify an immediate operand is the MOVe instruction. The most common use of such an instruction is to move a constant into a register (general, pointer, or index). In such cases, the non-immediate operand can be specified by a **reg** field, and the instruction takes the simple form shown in Fig. 2.20. The **w** field indicates if the operands (immediate as well as non-immediate) are eight bits ( $\mathbf{w} = 0$ ) or 16 bits ( $\mathbf{w} = 1$ ); if eight bits, the immediate operand occupies one byte in the instruction; otherwise it occupies two bytes and is stored "backwords." As an example, Fig. 2.21 shows an instruction that moves the value 1111 0000 0000 1111 to the 16-bit DI register.

A slightly more complicated immediate-operand instruction uses the **mod** and **r/m** fields instead of the **reg** field to specify the non-immediate operand. This is more general (non-immediate operand can be in memory) but requires an additional byte as illustrated in Fig. 2.22. Figure 2.23 shows an instruction that moves the value 1111 0000 0000 1111 into a word in memory in the data segment at the offset contained in DI.

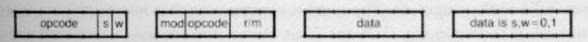

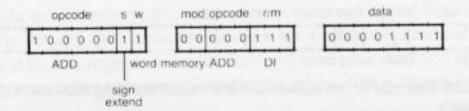

Since two-operand instructions have only one w field, either both operands must be eight bits or both must be 16 bits. However, immediate operands are frequently small numbers that don't require 16 bits. This is particularly true of immediate operands used with addition, subtraction, and comparison instructions; it is less true of immediate operands used with logical instructions. It follows that we could reduce the size of immediate-operand instructions if we didn't have to use 16 bits to house small numbers. To accomplish this, some of the immediate-operand instructions (additions, subtractions, and comparisons) contain an s field (s means sign-extend). This field only has significance for 16-bit operands ( $\mathbf{w} = 1$ ) and signifies whether all 16 bits of the immediate operand are contained in the instruction ( $\mathbf{s} = 0$ ) or whether only the eight least significant bits are contained in the instruction and must be sign-extended to form the 16-bit operand ( $\mathbf{s} = 1$ ). This form is illustrated in Fig. 2.24.

Figure 2.25 shows an example of such an instruction. In this example, the value 0000 0000 0000 1111 is added to the contents of a word in memory and the

Fig. 2.24 Immediate-operand instruction containing s field.

Fig. 2.25 Example of immediate-operand instruction containing an s field.

result placed back into the memory word. The memory word is in the data segment at the offset contained in DI. Note that one byte is eliminated by having the s field.

# Comments about Operand-Addressing Modes

After having read and understood the operand-addressing modes just described, you might be asking the following questions:

- 1. Do I really have to fill in the mod, r/m, reg, w, s, d, etc., fields every time I want to use an instruction that has operands?

- 2. Why are there so many memory-addressing modes?

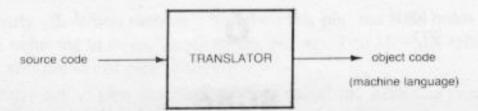

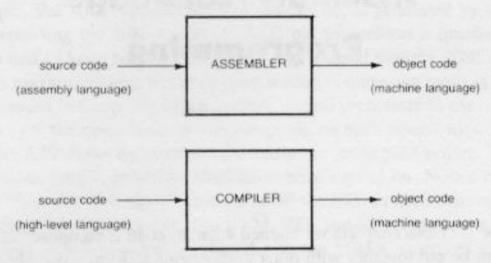

The answer to the first question is NO, unless you are of the conviction that the only proper way to write a program is in terms of 1's and 0's. But if you believe in automatic programming aids such as assemblers or compilers, you'll never have to look at a **mod**, **r/m**, **reg**, etc., field again; any decent assembler and every compiler will make these details invisible to you.

To understand the answer to the second question, you will recall that the 8086 was designed so that a program written in a high-level language could be translated into efficient code. Typical high-level language features were examined to determine what kinds of operand-addressing modes would best support them. Some of these features will now be discussed.

Most programming languages have the concept of simple variables and arrays. A *simple variable* is a variable that represents a single value; an *array* is a variable that represents a sequence of values. Consider an assignment statement typical of the kind found in many high-level languages.

$$A(I) = X$$

This statement is read "Ith element of A becomes X." It could be translated into code that moves the contents of the memory location corresponding to the simple variable X into a register, say BL, and then moves the contents of BL into the memory location corresponding to the Ith element in the array A. Assume that X is the contents of the memory location at offset 0FF0 (hexadecimal) in the current data segment. Furthermore, assume A(0), the first element of the array A, is at offset 0FF1 in that segment. The machine instruction that moves (the contents of) X into BL is shown in Fig. 2.26 (a). This utilizes the special case of **mod** and **r/m** chosen for direct memory addressing. Since accessing of simple variables such as

X is a frequent occurrence, it is not surprising that a special addressing mode was provided. The machine instruction that moves the contents of BL into A(I) is shown in Fig. 2.26 (b). Here it is assumed that the value of the index I already exists in an index register. Such array accesses point out the need for the indirect memory-addressing mode "index register + displacement." Assignments of the form A(I) = B(J) point out the need for at least two index registers, each with the addressing mode just mentioned, specifically "SI + displacement" and "DI + displacement." Accesses to array elements such as A(I+2) present no additional complication; the displacement field of Fig. 2.26 (b) would merely contain 0FF3, the offset of A(2), instead of the offset of A(0).

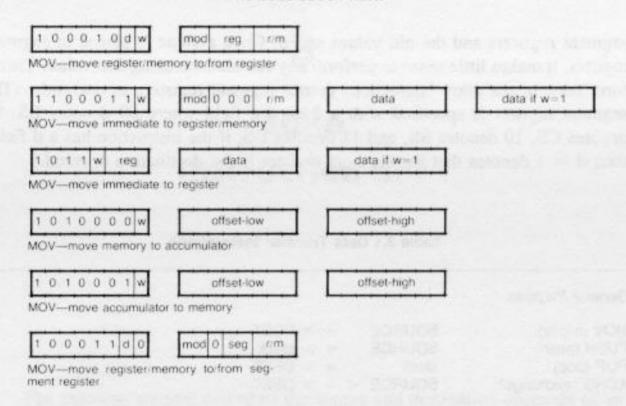

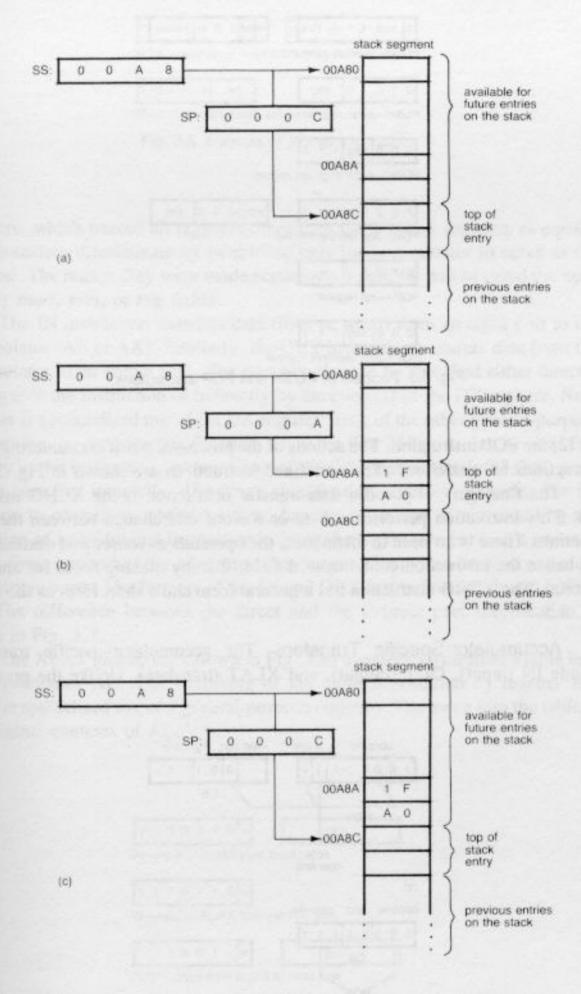

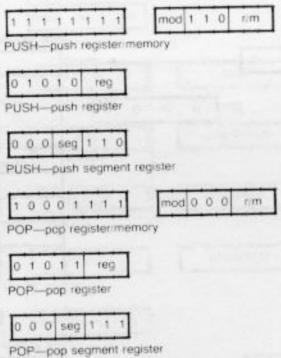

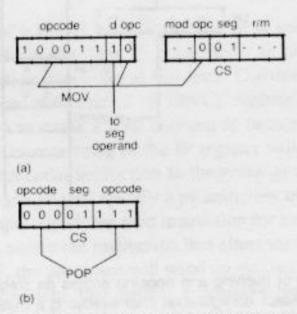

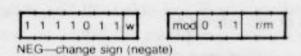

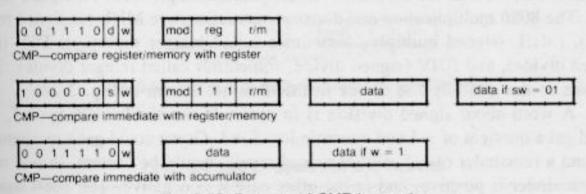

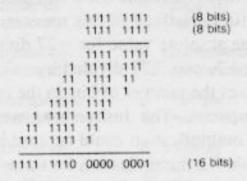

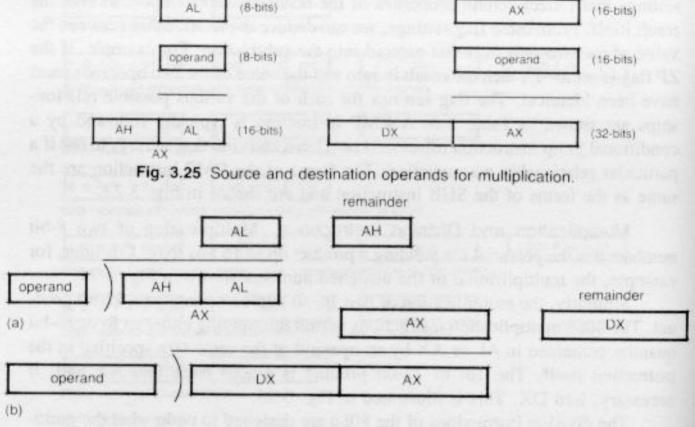

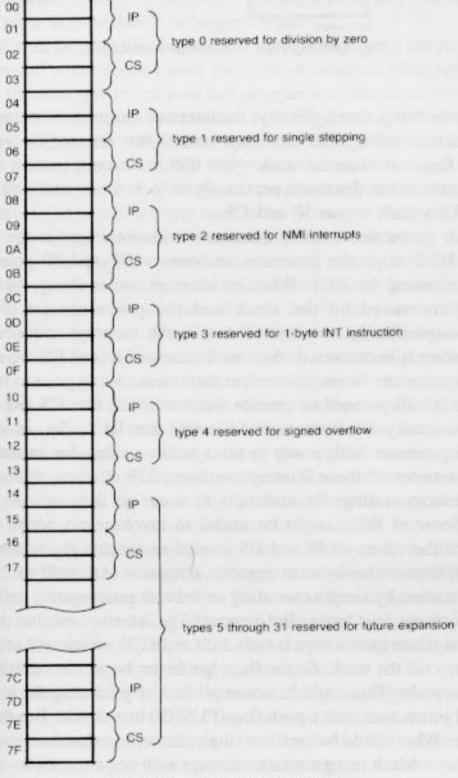

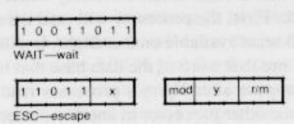

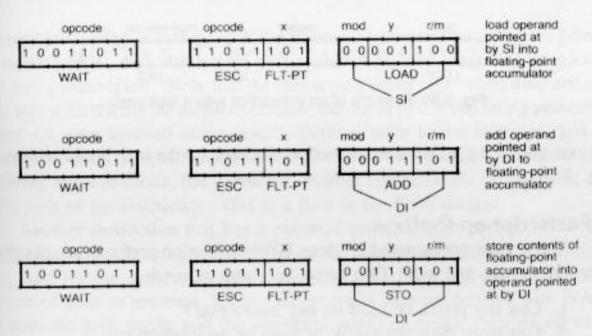

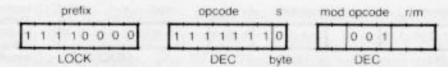

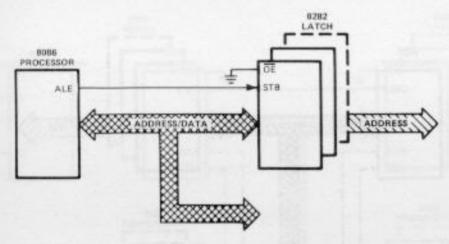

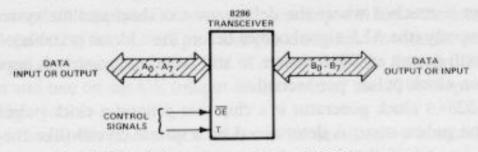

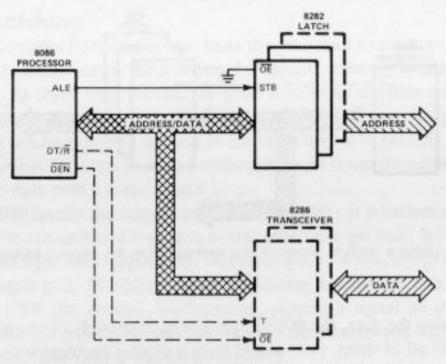

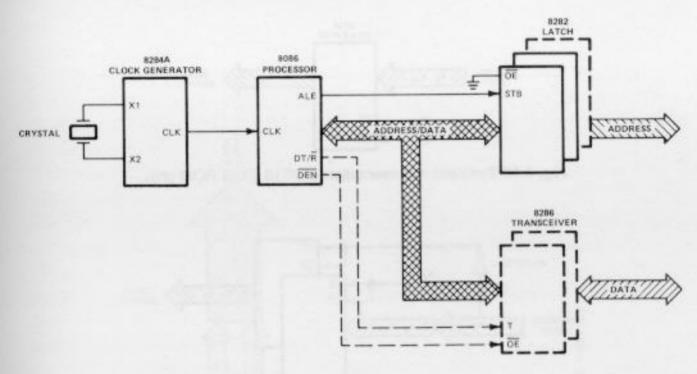

Fig. 2.26 Machine instruction for A(I) = X. (a) Moving X to BL. (b) Moving BL to A(I).